## 省電力セルフタイム回路に関する研究

岩田 誠1\* 宮城 桂1

三宮秀次2 西川博昭2

(受領日: 2013年5月7日)

「高知工科大学情報学群 〒782-8502 高知県香美市土佐山田町宮ノ口185

<sup>2</sup> 筑波大学システム情報系 〒 305-8573 茨城県つくば市天王台 1-1-1

\* E-mail: iwata.makoto@kochi-tech.ac.jp

**要約**:将来の情報化社会をより持続可能な社会へ導くためには、情報通信機器の省エネルギー化は欠かすことのできない技術の一つである。本研究では、大規模集積(LSI: Large Scale Integration)システムの低消費電力化技術に着目して、クロックを用いない独創的なセルフタイム回路を活用した省電力化技術に関して検討を行っている。

本稿では、セルフタイム回路によって、従来システムよりも実時間かつ細粒度で電力制御が可能なことを示し、この電力制御方式を適用して試作したデータ駆動プロセッサ LSI チップの実測結果を通してその有効性を示す。さらに、無線アドホックネットワーク上での実際の UDP/IP トラフィックを対象とした通信処理ノードに応用し、通常のセルフタイム回路によるプロセッサ実装に比較して約13%に低消費電力化できることを示す。これによって、実用的な環境でも実効的に省電力化が可能なことが実証された。

#### 1. はじめに

大規模集積回路(LSI)の微細加工技術の進展に伴って、今やCMOSトランジスタのゲート長は10nmに近づきつつあり、1つのLSIチップに数十億トランジスタを集積化できる時代になっている。この集積化可能なトランジスタ数の増大に伴って、LSIチップの消費電力は増加する傾向にあり、様々な低消費電力化技術の研究開発が進められている1.21。これらの技術によって、例えば、データセンター等の電力コスト削減や、スマートフォン等のバッテリ持続時間の延長が可能になり、様々な情報通信システムをインフラとする現代の情報化社会の持続可能性の向上に寄与している。

現行の多くのLSIチップは、数白MHzから数GHz の高速クロックに同期して動作しており、このクロッ ク信号の伝搬に要する電力消費が全体の30%程度を 占めるという報告もある<sup>3)</sup>。このため動作していない回路ブロックにはクロック信号の供給を遮断するクロックゲーティング技術が用いられている。これに対して、筆者らグループは、隣接する回路ブロック間でのみデータ転送要求 (send) 信号と許可 (ack) 信号を授受するセルフタイム回路に着目して長年研究を進めてきた。セルフタイム回路は大域的なクロック信号を用いないため、クロック信号伝搬に要する電力がそもそも不要であり、省電力化が可能であるからである。1997年には、セルフタイム回路による商用マルチプロセッサチップのLSI化に成功し、当時、世界一の電力当りの性能(10GOPS/2W)を達成した<sup>4)</sup>。

一方、回路ブロック自体の消費電力については、 その回路に要求される動作速度に応じて動的に供 給電圧(およびクロック周波数)を変更する、動的 電圧周波数制御 DVFS (Dynamic Voltage Frequency Scaling)技術<sup>50</sup>が用いられている。また、昨今の微細化されたトランジスタでは、動作していない時でも微小な漏れ電流が流れて無駄に電力を消費するため、非動作時には電力供給そのものを遮断するパワーゲーティング PG(Power Gating)技術<sup>60</sup>が使われている。しかしながら、これらの制御にはオーバヘッドを伴うため、従来型の商用 LSI チップでは、チップ単位ないしはプロセッサコア単位のような比較的規模の大きな回路に対してしか適用されていないのが実情である。

本研究は、セルフタイム回路が本来有している 省電力特性に加えて、供給する電力を細かく実時間 制御する機構を導入することによって、さらなる省 電力化が可能なセルフタイム回路技術を確立する ことを目標としている。以下本稿では、セルフタイ ム型パイプライン STP (Self-Timed Pipeline) 回路の ための実時間電力制御方式を提案し、その消費電力 特性について議論する。その後、提案回路を適用し た試作 LSI プロセッサチップの実測結果を通して、 本提案回路の有効性を示す。

## 2. STP の実時間細粒度電力制御方式

一般には、プロセッサ内の処理負荷は、プログラムに内在する並列度、および、外部からの処理要求トラフィックに応じて、時々刻々変動する。本稿で提案する実時間細粒度電力供給方式は、このような処理負荷の変動状況に応じて適応的に電圧制御ならびにパワーゲーティングを実現し、可能な限り消費電力を抑えることを目的としている。

本章では、セルフタイム型パイプラインの自律 的な動作様式について簡単に紹介した後、この動作 様式を活用した実時間細粒度電力制御方式につい て述べる。

#### 2.1 セルフタイム型パイプライン STP

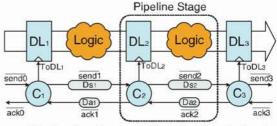

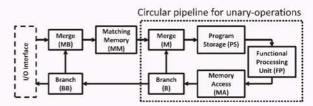

STPは基本的には図1のように構成される。各パイプラインステージは、パイプラインレジスタとして動作するデータラッチ、処理回路、および、データ転送制御回路として動作する一致記憶フリップフロップ(Coincidence flip-flop: C素子)により構成される。データはタグ付きのパケット形式で取り扱われ、STP内では各パケットはステージ間の制御信号(send 信号、ack 信号)の伝達によって自律的に移動する。具体的には、

- (パケットの転送開始) C素子が前方ステージ へ send<sub>i-1</sub> 信号を伝達する。同時に、データラッ チが前方ステージへパケットを送信する。

- 2. (ハンドシェイク) C素子は send<sub>i-1</sub> および ack<sub>i</sub>

DL: Data Latch

C: Transfer Control Circuit

Ds: Delay Element of send Signal Da: Delay Element of ack Signal

図1.セルフタイム型パイプラインの基本構成

信号が到着すると、データラッチ DL<sub>i</sub> を開ける。結果、パケットが転送される。

- (ack 信号遷移) 同時に C 素子は、ack<sub>i-1</sub> 信号 を後方ステージに伝達し、後続パケットの転送 を許可するとともに、

- (send 信号遷移) send<sub>i</sub> 信号を前方ステージへ 伝達し、前方ステージへのパケット転送を開始 する。

- 5. パケットがある限り上記1~4を繰り返す。

以上のようなパイプライン段間の局所的な転送制御により、STPには、(a)局所的な信号伝達のみによって動作時にだけスイッチング電力を消費する省電力特性や、(b)負荷の変動に対する自律緩衝能力(エラスティック能力)といった、LSI実現に適した特性がある<sup>4)</sup>。

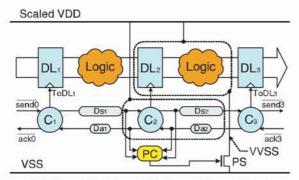

#### 2.2 ステージ単位パワーゲーティング

STP内のステージ間で授受される send 信号と ack 信号は、当該ステージにおけるパケットの有無を表している。これらの信号を活用すれば、ステージ毎に電力の供給/遮断を制御することが可能になる。すなわち、動作していないステージの電源線をパワースイッチにより on/off すれば、プロセッサコア単位よりも細かなパイプラインステージ単位で無駄な漏れ電流を防ぐことが可能になる。図2にその回路図を示す。パワースイッチとして、漏れ電流が比較的少ない、高しきい値 nMOSトランジスタを用い、これを処理回路とグラウンド線 VSS との間に挿入する。そして、このパワースイッチを send 信号と ack 信号に基づいて制御する回路 PC を追加すれば良い。

一般には、電源遮断された回路ブロックから電源 供給されている回路ブロックへ不安定な信号値が伝 搬して回路が誤動作するのを防ぐために、これらの 間には、分離セル (isolation cell) を挿入する必要が ある。しかし、STP の場合、データラッチ回路の一

PS: Power Switch

PC: Power Control Circuit

図 2. STP のステージ単位パワーゲーティング

図 3. STP の動的電圧制御機構

部が分離セルの機能を果たすことができ、分離セル専用の追加回路が不要であるという利点もある。

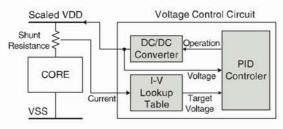

### 2.3 動的電圧制御機構

STPの消費電力は、パイプライン内のデータ流に 擾乱を与えるインタロックやフォワーディング機構 を導入しない限り、データ流量に比例するという素 直な特性を有している。これは、同期回路における クロック分配のように、データ流量とは無関係に消 費される電力がないためである。したがって、STP 内で消費される電流を観測することによって、その 時点のデータ流量、すなわち、処理負荷を観測で きる。トランジスタの動作速度は電圧に比例し、ス イッチング電力が電圧の二乗に比例することから、 観測した処理負荷に応じて電源電圧を昇降させれ ば、OSを介さずに省電力化が可能になる。STPの動 的電圧制御機構の基本構成を図3に示す。この構成 では、観測した消費電流から適切な目標電源電圧を 定め、PID制御により電圧昇降値を安定的にフィー ドバック制御する。

通常、同期回路では、電圧の昇降に伴ってクロック周波数も昇降させる必要があり、クロック信号用の位相同期回路 PLL(Phase Locked Loop)が追加的に必要になる。この PLL によるクロック周波数の昇降には通常数十 μs を要するため、それより短い時間での電圧制御ができない。これに対して、STPにおいては、PLL が不要であり、かつ、OS を介さず電圧を制御できるため、実時間での電圧制御が可

図 4. 実時間細粒度電力制御方式の等価回路モデル

能になる。さらに、クロック周波数の昇降を待つ必要がないため、回路が誤動作しない範囲の小さな電圧昇降幅、あるいは、緩やかな電圧昇降を保証すれば、電圧昇降の過渡的な期間でも回路の動作を停止せずにプログラムを継続的に実行することが可能になる。

以上に述べたように、STPの自律的な動作原理を活用することによって、リーク電力を抑えるパワーゲーティング技術、ならびに、スイッチング電力を抑える電圧制御技術のいずれにおいても、より細やかな省電力化が可能になる。

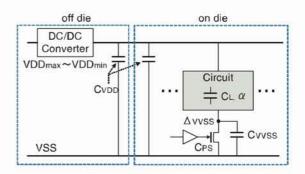

#### 2.4 提案方式の省電力効果のモデル化

パワーゲーティングは、電源遮断時にリーク電力を抑えられるが、一方で、パワースイッチ PSのon/offに要するスイッチング電力および PS オン時に流れる突入電流が電力オーバヘッドとなる。また、動的電圧制御は、処理負荷に応じて対象回路のスイッチング電力を抑えられるが、一方で、電源電圧 VDD の昇降時に対象回路の負荷容量に応じた充放電電流が発生する。

図4にその等価回路を示す。この回路では、PSのスイッチング電力量  $E_{PS}$  は式(1)で表せる。

$$E_{PS} = C_{PS} \times VDD^2 \tag{1}$$

ただし、 $C_{PS}$  は PS の寄生容量である。

また、PS オン時の突入電流による電力量  $E_{rush}$  は 文献  $^{7}$  に基づき次式で表せる。

$$E_{rush} = \left(C_{VVSS} + \frac{1}{2}C_L\right) \times VDD \times \Delta_{VVSS}$$

(2)

ただし、 $C_{VVSS}$  と  $C_L$  はそれぞれ仮想グラウンドおよび制御対象回路の容量成分である。また、 $\Delta_{VVSS}$  は PS オフ時の仮想グラウンドの電位であり、これは電源遮断の期間(スリープ時間)が長くなるほど VDD に漸近する。

よって、スリープ時間が長くなればなるほど、削減できるリーク電力量が増えるが、逆に、短いと削減できるリーク電力量よりもオーバヘッド電力量が大きくなり、パワーゲーティングの効果が得られないことになる。すなわち、削減可能なリーク電力量とオーバヘッド電力量が拮抗するスリープ時間を損益分岐点として、パワーゲーティングの効果の有無が決まる。この損益分岐スリープ時間BET(Break Even sleep Time)は、式(1)(2)より、次式で近似できる。

$$BET = \frac{E_{PS} + E_{rush}}{P_{leak}} \tag{3}$$

ただし、 $P_{leak}$ は、対象回路において電源遮断時に削減できるリーク電力である。

動的電圧制御に関しても同様に、電力量の観点で損益分岐点が存在する。基本的には、電圧降下後に電力量削減が可能なため、降圧(/昇圧)時に電源ラインの放電(/充電)に要するオーバヘッド電力量に対して、制御対象回路の削減可能な電力量が拮抗する点が損益分岐点になる。すなわち、1回の電圧降下に対して、対象回路が何度動作すると省電力効果が得られるかということになる。よって、これを損益分岐処理負荷BEPL(Break Even Processing Load)と呼ぶ。このBEPLは次式で近似できる。

$$BEPL = \frac{C_{VDD}}{C_L \times \alpha} \tag{4}$$

ただし、 $\alpha$ は、制御対象回路を構成するトランジスタのスイッチング確率の平均値を表す。すなわち、制御対象回路が 1 度動作する時に、(全トランジスタ数× $\alpha$ ) 個のトランジスタが動作するという仮定である。

### 3. 省電力性能の評価

本研究では、実時間細粒度電力制御が可能な STP の実用性を実証的に評価するために、65nm CMOS プロセスを用いて試作したデータ駆動プロセッサ LSI<sup>8,9)</sup> に提案方式を適用し、その省電力性能を評価した。

本章では、試作プロセッサについて簡単に紹介した後、その実測値ならびに回路シミュレーション結果を総合して、省電力特性を示す。さらに、具体的なアドホックネットワーク上のトラフィックログに基づいて、通信プロトコル処理をプロセッサ上で実行した場合の実効的な省電力化効果を示す。

図 5. 試作データ駆動プロセッサの STP 構成

図 6. 試作 ULP-CUE のレイアウト

#### 3.1 試作データ駆動プロセッサの構成

試作した 32bit データ駆動プロセッサ ULP-CUE は、13 段の環状パイプラインにより構成されている。図5 に本プロセッサのブロック図を示す。図中の各 STP ステージには以下の機能が実装されている。

- MB: 外部からの入力パケットおよび内部を周回するパケットを合流させる機能

- MM: 二項演算命令の実行に必要なオペランド の組を検出する待合せ記憶機能

- M: 単項演算命令の実行時に周回するパケット の合流機能

- PS: 命令を取り出すためのプログラム記憶機能

- FP: 指定された演算を実行する機能

- MA: メモリアクセス命令を実行する機能

- B: 演算子のオペランド数に応じてパケットを 分流させる機能

- **BB**: 外部への出力パケットあるいは内部を周回 するパケットを分流する機能

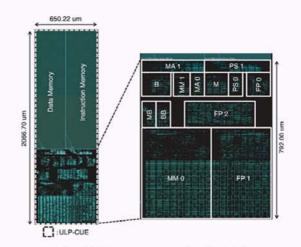

これらの各 STP ステージは、図 6 に示すように チップ上に配置・配線され、LSI 化された。ただし、 パワースイッチ PS による電圧降下が VDD の 5%以 下となるように、nMOS トランジスタのゲート幅を 調整して、標準セルライブラリのリキャラクタライ ズを施した上で、タイミング検証等を実施して設計 されている。

図 7. 各ステージのパワーゲーティング効果 (0.8 V, 25 ℃).

#### 3.2 提案方式の省電力特性

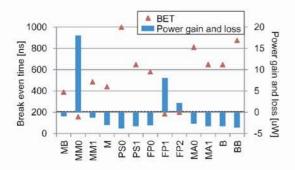

図 6 からも判るように、各ステージの面積は異なっている。つまり、各ステージの負荷容量  $C_L$  は異なり、式 (3) の損益分岐スリープ時間 BET も異なる。しかし、試作 LSI チップでは、式 (3) の各パラメタを直接的に実測することは困難であるため、レイアウトデータの SPICE シミュレーションにより求めた。特に、式 (2) の突入電力量は、スリープ時間によって異なるため、いくつかの条件で複数回 SPICE シミュレーションを実施して、求めた。

図7に各ステージのパワーゲーティングの効果を示す。図中の三角のプロットは、各ステージのBETを示している。その結果、13段全てのBETは250nsの時の各ステージの電力削減効果を示している。MMOステージのBETが159nsで最短となっている。これは、MMOの面積が最も大きいことからも類推できる。また、PSOステージのBETが998nsで最長となっており、MMOのBETの約5倍になっている。よって、アプリケーションプログラムの平均的な処理負荷に応じて決まるスリープ時間よりもBETが短いステージのみパワーゲーティングを有効にすれば、プロセッサ全体のリーク電力削減効果を上げることが可能になる。

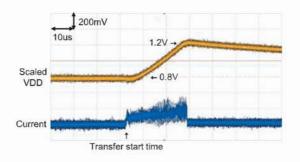

動的電圧制御の効果に関しては、試作プロセッサの実測により、その効果を確認した。図8は、処理負荷を調整可能なテストプログラムを用いて、VDDを 0.8V から 1.2V に昇圧した時の実測波形である。図中上部の波形がVDD、下部の波形がその時の消費電流である。この消費電流には、式(4)における $C_{VDD}$  と $C_L$  の両者に係る充放電電流が含まれている。一方で、プログラムを動作させずに、VDD を 0.8V から 1.2V に昇圧した時の電流を測定すれば、 $C_{VDD}$  に係る電流のみが観測でき、図8の消費電流との差分としての $C_L$ を求めることが可能になる。

図 8. VDD 昇圧時の消費電流波形の実測例 (25℃).

図 9. 試作プロセッサの損益分岐負荷 BEPL (0.8 V 1.2 V, 25 ℃).

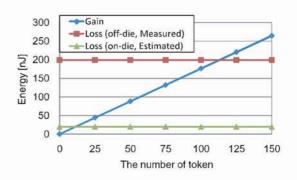

その結果を図9に示す。図中四角のプロットが電源線の充放電エネルギーを、ひし形のプロットが電圧降下に伴い削減できる電力を示している。このグラフから、試作チップでは、113パケット以上を実行すると電力削減効果が得られることがわかる。

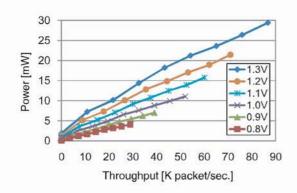

試作プロセッサ LSI の実効的な消費電力特性を確認するために、UDP/IP 通信プロトコル処理プログラムを実行した時の性能と消費電力を実測した。図 10 はその測定結果である。横軸は、512Byte のUDP/IP パケットの処理レートを示し、縦軸は消費電力を示している。電源電圧 VDD を 0.8V~1.3V まで変化させた結果、いずれの場合も消費電力は処理負荷に対してほぼ線形に増減することが確認された。処理負荷がゼロ近辺では、消費電力もほぼ 0Wになっていることが判る。これは、同期回路のようにクロック分配のための余分な電力消費がないことの証左である。

また、図10の実測結果から、0.8V時にUDP/IPパケット換算で最大29 K packet/s が処理可能である。この時、標準電圧1.2Vで動作させた場合と比較すると最大で消費電力を38%に削減できることを示している。このことから、BEPLを考慮すると、平均32.7 KHz以下で電圧昇降すれば、動的電圧制御の効果が得られることになる。もし、試作プロセッ

図 10. 試作プロセッサの性能-電力特性 (25℃).

図 11. VDD 昇圧時間とその間の処理性能 (25°C).

サ LSI に DC-DC コンバータを搭載すれば  $C_{VDD}$  は 1割程度に低減できるという報告  $^{51}$  もあり、この値を想定すると、電圧昇降の頻度を 336KHz に上げても電力削減効果が見込めることになる。

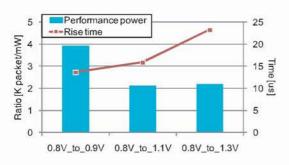

前章にも述べたように、STPの場合、電圧昇降の 過渡的な期間でもプログラムの実行を継続すること が可能である。試作プロセッサ LSI でも継続実行が 可能なことを確認した。図11 は、0.8V から昇圧し たときの昇圧時間と、その間に処理可能な UDP/IP パケット数を実測して電力当りの性能を求めた結果 である。この結果から、処理性能的にも利点がある ことが実証された。

図 10 の測定結果は、定常的な UDP/IP トラフィックを前提としたものであるが、実システムでトラフィックは変動する。本研究では、現実的な条件での実効的な省電力効果を明らかにするために、文献 <sup>10)</sup> で提案されているアドホックネットワーク環境を想定したネットワークシミュレーション結果から得られた UDP/IP パケットログを対象にして、ULP-CUE の消費電力を評価した。

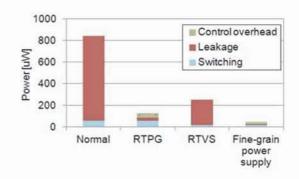

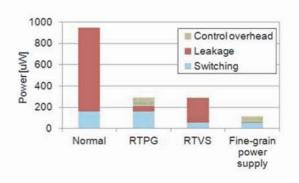

54 M bit/s および 162 M bit/s の無線インタフェースを前提として、パワーゲーティングのみを適用した場合、動的電圧制御のみを適用した場合、両者を併用した場合の消費電力を図 12 および図 13 に示す。図 13 では、パワーゲーティングの適用によっ

図 12. 実トラフィック処理時の電力比較 (54 M bit/s, 25 ℃).

図 13. 実トラフィック処理時の電力比較 (162 M bit/s, 25 ℃).

てリーク電力が 48μW に低減されている。これは 通常の STP 構成と比較して、リーク電力を 6%にま で削減できている。また、動的電圧制御の適用に よって、スイッチング電力は 51.7μW に低減できて いる。これは通常の STP 構成と比較すると 32%の 電力に抑えられている。両者を併用した提案方式で は、ULP-CUEの電力を 13%にまで低減できている。 これは、0.8V 時にはパワースイッチ PS のスイッチ ングエネルギーも減るため、相乗的な省電力効果も 含まれているためである。

#### 4. おわりに

本稿では、セルフタイム回路が本来有している 省電力特性に加えて、供給する電力を細かく実時間 制御する機構を導入することによって、さらなる省 電力化が可能なセルフタイム回路技術についての 研究成果の一端を紹介した。

具体的には、セルフタイム型パイプライン STP (Self-Timed Pipeline) 回路のための実時間電力制御方式を提案し、その消費電力モデルについて議論した。その後、提案回路を適用した試作 LSI プロセッサチップの実測結果を通して、本提案回路の有効性

を示した。無線アドホックネットワーク上のUDP/IPトラフィックを対象とした通信処理ノードに応用し、通常のセルフタイム回路によるプロセッサ実装に比較して約13%に低消費電力化できることを示した。これによって、本提案技術が、実用的な環境でも実効的に省電力化が可能なことが実証されたと考えている。

本稿で触れたデータ駆動プロセッサ LSI は、超低消費電力化ネットワーキングシステムを実現するための CREST 研究プロジェクトの一環として試作されたものでもあり、ネットワーキング方式、LSI プロセッサアーキテクチャおよびその LSI 回路実現法に至るまで省電力化を徹底することによって、総合的には従来システムに比較して、約 1/180 に低電力化できることも明らかになっている。その詳細については、文献 11) を参照されたい。

## 謝辞

本研究の一部は、科学技術振興機構 JST CREST、および日本学術振興会科研費の支援を受けて行ったものである。回路設計・シミュレーションは、東京大学大規模集積システム設計教育研究センターを通し、シノプシス株式会社、日本ケイデンス株式会社およびメンター株式会社の協力で行われたものである。

### 文献

- Proceedings of International Symposium on Low Power Electronics and Design, 2001-2012.

- Proceedings of International Symposium on Technology Innovation and Integration for Information Systems with Ultra-Low-Power, Mar. 2011.

- "Clock signal," http://en.wikipedia.org/wiki/Clock\_signal, May 2013.

- H. Terada, S. Miyata, and M. Iwata, "DDMP's: Self-Timed Super-Pipelined Data-Driven Processors," Proceedings of the IEEE, Vol.87, No.2, pp.282–296, Feb. 1999.

- W. Kim et al., "System Level Analysis of Fast, Per-Core DVFS Using On-chip Switching Regulators." IEEE 14th International Symposium on High Performance Computer Architecture, pp.123–134, 2008.

- 6) N. S. Kim, D. B. Blaauw, T. Mudge, K. Flautner, J. S. Hu, M. Jane, M. Kandemir, and V. Narayanan, "Leakage Current: Moore's Law Meets Static Power," IEEE Computer Mag., Vol. 36, No. 12, pp.68–75, Dec. 2003.

- Z. Hu, A. Buyuktosunoglu, V. Srinivasan, V. Zyuban, H. Jacobson, and P. Bose, "Microarchitectural Techniques for Power Gating of Execution Units," Proceedings of the 2004 International Symposium on Low Power Electronics and Design (ISLPED'04), pp.32–37, Aug. 2004.

- 8) S. Sannomiya, R. Kuroda, K. Aoki, K. Miyagi, M. Iwata, and H. Nishikawa, "Chip Multiprocessor Platform for Ultra-Low-Power Data-Driven Networking System: ULP-DDNS," Proceedings of the 2011 International Conference on Parallel and Distributed Processing Techniques and Applications(PDPTA'11), pp.428–434, July 2011.

- 9) 三宮, 青木, 宮城, 岩田, 西川, "超低消費電力化 データ駆動ネットワーキングプロセッサ ULP-CUE の試作とその評価," 情報処理学会論文誌コ ンピューティングシステム (ACS), Vol.6, No.1, pp.78–86, Jan. 2013.

- 10) K. Utsu, H. Sano, C. Chow, and H. Ishii, "Proposal of Load-aware Dynamic Flooding over Ad Hoc Networks," Proceedings of IEEE TENCON 2009, THU2, pp.1–6, Nov. 2009.

- 11) 西川,青木,三宮,宮城,岩田,宇津,石井, "超低消費電力化データ駆動ネットワーキング システムとその評価,"電子情報通信学会論文誌 B, Vol.J96-B, No.6, Jun. 2013. (掲載予定)

# A Study on Low-Powered Self-Timed Pipeline Circuit

## Makoto Iwata<sup>1\*</sup> Kei Miyagi<sup>1</sup>

## Shuji Sannomiya<sup>2</sup> Hiroaki Nishikawa<sup>2</sup>

(Received: May 7th, 2013)

<sup>1</sup> School of Information, Kochi University of Technology 185 Tosayamadacho-Miyanokuchi, Kami, Kochi, 782-8502, JAPAN

<sup>2</sup> Faculty of Engineering, Information and Systems, University of Tsukuba Tsukuba Science City, Ibaraki 305-8573 JAPAN

\* E-mail: iwata.makoto@kochi-tech.ac.jp

**Abstract:** Saving of energy in diverse information communication systems is indispensable for leading future sustainable information society. Our study focuses on low power technology for large scale integration circuit systems and investigates a low-power technique of self-timed (clockless) pipeline circuit by incorporating both commonly used voltage scaling and power gating techniques.

This paper discusses that self-timed pipeline makes it possible to control power supply more finely and in real time, compared with conventional clock-based systems, and then shows its effectiveness through experimental evaluation results of a prototype data-driven network processor LSI designed with the proposed low-power self-timed pipeline circuit. In case of typical UDP/IP traffic of a wireless ad hoc network, total power can be reduced to about 13 % compared with the original STP-based processor.