## Defect-oriented Built-In Self-Test for Analog Mixed-Signal Circuits

by

## TANG Xiaobin

Student ID Number: 1248003

A dissertation submitted to the Engineering Course, Department of Engineering, Graduate School of Engineering, Kochi University of Technology, Kochi, Japan

in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Assessment Committee: Supervisor: Prof. TACHIBANA Masayoshi Co-Supervisor: Prof. MITSUYAMA Yukio Co-Supervisor: Assoc. Prof. HOSHINO Yukinobu Prof. IWATA Makoto Prof. HAMAMURA Masanori

September 2023

## Abstract

#### Defect-oriented Built-In Self-Test for Analog Mixed-Signal Circuits

With the development of advanced technology, the scale of circuit becomes larger and larger, and the testing technology becomes more and more complex. In circuit design, adding test circuit is a cost-saving way, whether it is prototype circuit or mass production circuit. In prototype circuit, the built-in self-test can help the design quickly locate the fault when testing the circuit. When the circuit is mass-produced, part of the test circuit is reserved, and the circuit performance can also be detected to eliminate defective products.

However, there are still many analog mixed-signal circuits without corresponding testing strategies. Therefore, the circuits under tested in this dissertation have two characteristics, one is that the circuit is a mixed-signal circuit; the other is that the circuit has a rarely relevant test strategy. At the same time, the purpose of this dissertation is to combine the built-in self-test technology to detect the fault of these circuits.

In the first part of this dissertation, a built-in self-test (BIST) scheme for detecting catastrophic faults in bootstrapped switches is proposed. The clock signal and the gate voltage of the sampling Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) are taken as the observation signals in the proposed BIST scheme. Usually, the gate voltage of the sampling MOSFET is greater than or equal to the supply voltage when the switch is turn on, and such a voltage is not suitable for observation. To solve this problem, a low power supply voltage is provided for the bootstrapped switch to obtain a suitable observation voltage. The proposed BIST scheme and the circuit under test are realized with transistor level. The proposed BIST scheme was simulated by Simulation Program with Integrated Circuit Emphasis (SPICE). The simulated fault coverage is approximately 87.9% with 66 test circuits.

In the second part of this dissertation, a built-in self-test scheme for detecting catastrophic faults in dynamic comparators. In this scheme, a feedback loop is designed using the characteristics of the comparator. By monitoring the voltage in the feedback loop to determine the presence of circuit fault. The proposed BIST scheme and the circuit under test are realized with transistor level. The proposed BIST scheme was simulated by SPICE. The simulated fault coverage is approximately 87.8% with 90 test circuits. To further verify the effectiveness of the propose BIST scheme, six faults were injected into the real circuit. The test results are consistent with the simulation results.

In the third part of this dissertation, a compact window comparator for extreme voltage is proposed. Extreme voltage means that the voltage is close to the ground or close to the supply voltage. However, detection of extreme voltage is suffered by the threshold voltage of a transistor. This paper proposes a new compact window comparator, which can be used to detect extreme voltage. In this window comparator, a source follower is used to translate the extreme voltage to the voltage suitable for detection. The test results verify the proposed compact window comparator in Rohm 180nm Complementary Metal Oxide Semiconductor (CMOS) technology.

## Contents

| Abstract                                                           | .I  |

|--------------------------------------------------------------------|-----|

| ContentsI                                                          | Π   |

| List of FiguresI                                                   | V   |

| List of TablesV                                                    | /Ι  |

| 1 Introduction                                                     | 1   |

| 1.1 An Overview of BIST Technology for Analog Mixed-signal Circuit | 1   |

| 1.2 Objectives of this Dissertation                                | 2   |

| 1.3 Fault modeling for Circuits                                    | 2   |

| 1.4 Dissertation Organization                                      | 3   |

| Reference                                                          |     |

| 2 A BIST Scheme for Bootstrapped switches                          | 5   |

| 2.1 Introduction                                                   |     |

| 2.2 The Circuit under Test                                         | 6   |

| 2.3 The proposed BIST Scheme                                       | 7   |

| 2.4 Simulation Results                                             | 9   |

| 2.5 Discussions and Conclusion 1                                   | 2   |

| Reference1                                                         |     |

| 3 A BIST Scheme for Dynamic Comparators 1                          | 6   |

| 3.1 Introduction                                                   |     |

| 3.2 The Circuit under Test1                                        | 7   |

| 3.3 The proposed BIST Scheme1                                      | 8   |

| 3.4 Simulation Results1                                            | 9   |

| 3.5 Test results                                                   |     |

| 3.5.1 The circuit under test                                       | \$4 |

| 3.5.2 Test results                                                 | 15  |

| 3.6 Discussions and Conclusion                                     | 17  |

| Reference4                                                         |     |

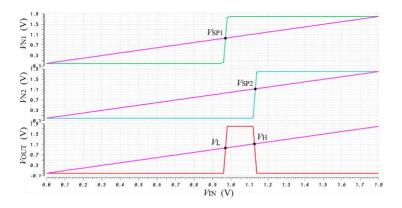

| 4 A Compact Window Comparator for Extreme Voltage                  | 51  |

| 4.1 Introduction                                                   | 51  |

| 4.2 Conventional window comparator5                                | 52  |

| 4.3 Proposed window comparator                                     | 63  |

| 4.4 Simulation results5                                            | 64  |

| 4.5 Test Result                                                    | 55  |

| 4.6 Conclusion5                                                    | 57  |

| Reference5                                                         |     |

| 5 Conclusions 5                                                    | ;9  |

| Acknowledgements6                                                  | 51  |

| List of Publications6                                              | 52  |

# List of Figures

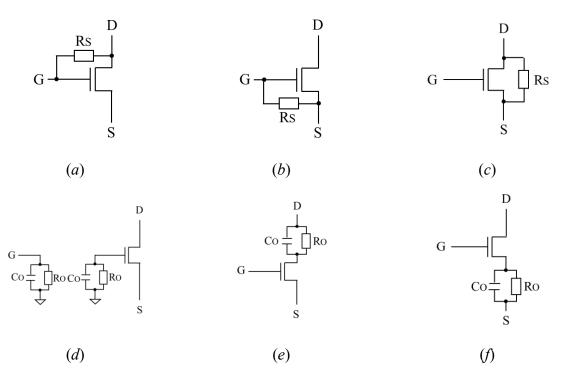

| Figure 1.1 The fault types simulated in this dissertation. (a) the gate-drain short (GDS) of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| the transistor; (b) the gate-source short (GSS) of the transistor; (c) the drain-source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| short (DSS) of the transistor; (d) the gate open (GO) of the transistor; (e) the drain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| open (DO) of the transistor; ( <i>f</i> ) the source open (SO) of the transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

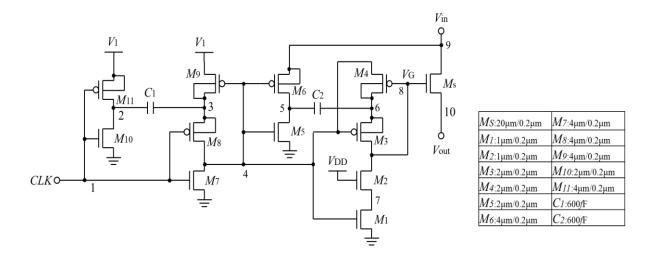

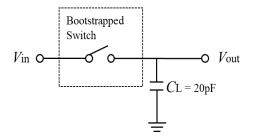

| Figure 2.1 The bootstrapped switch in [17] and the designed size of elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

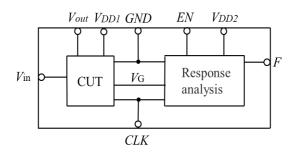

| Figure 2.2 The proposed BIST schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

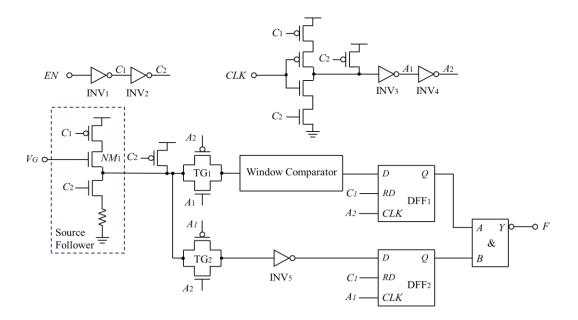

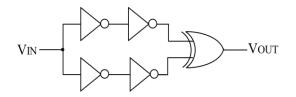

| Figure 2.3 The schematic of the response analysis module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 2.4 The schematic of the window comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 2.5 The performance simulation schematic for bootstrapped switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

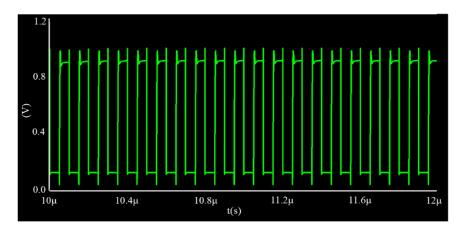

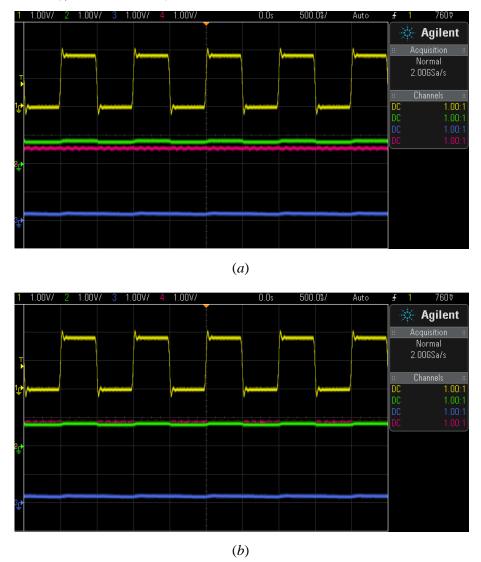

| Figure 2.6 The output signal by transient simulation (a) fault-free; (b) fault with GSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| with the $M_1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 2.7 The gate voltage of M1 with the fault of GO of M1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

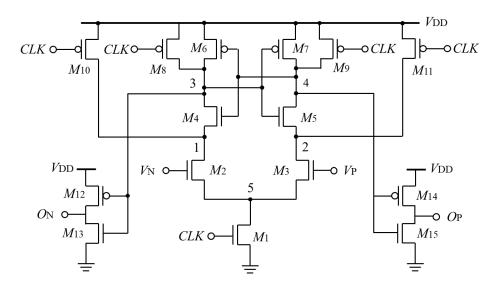

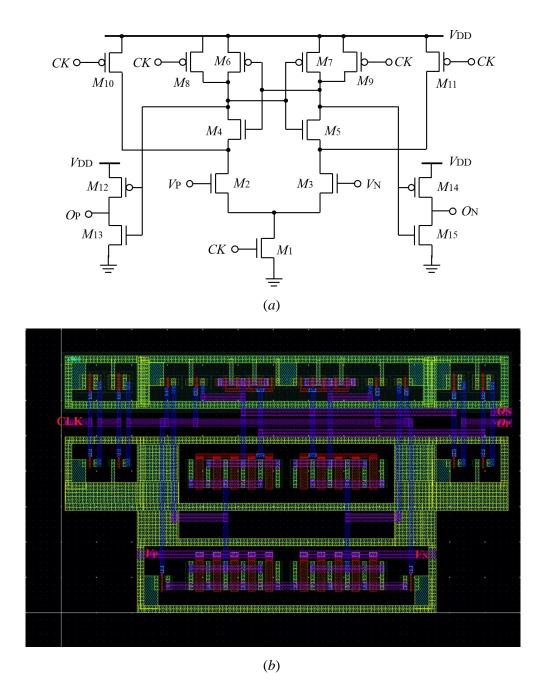

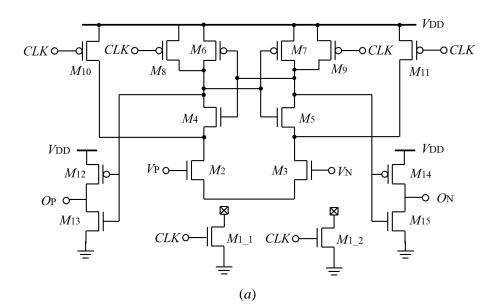

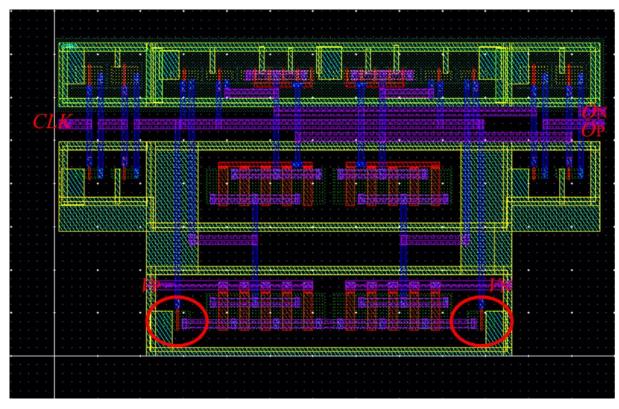

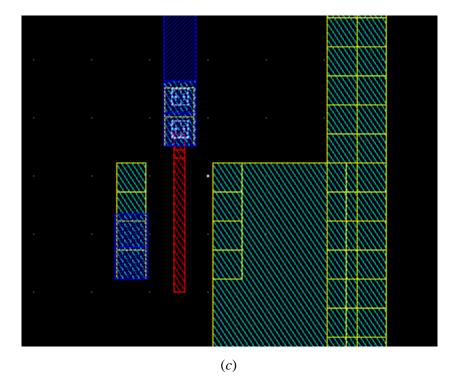

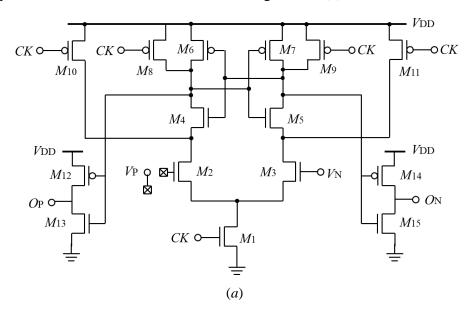

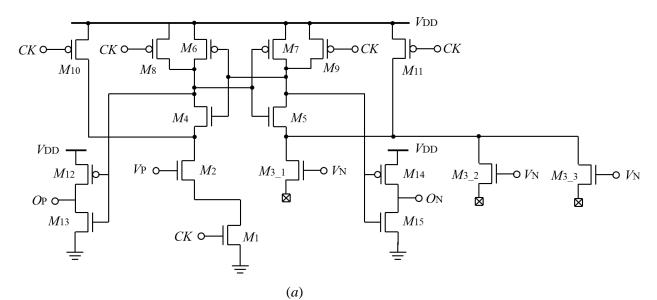

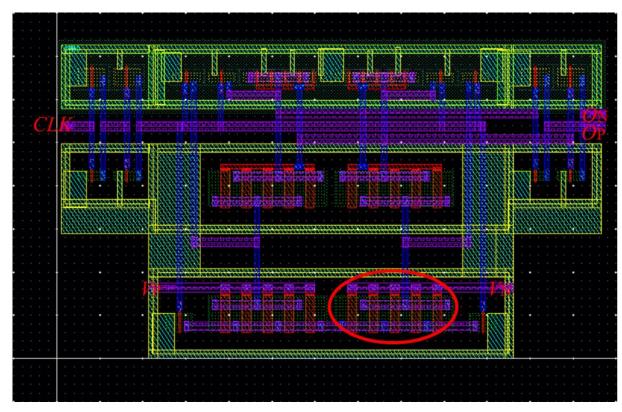

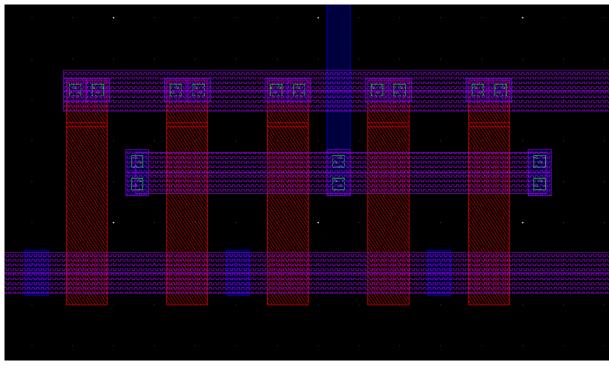

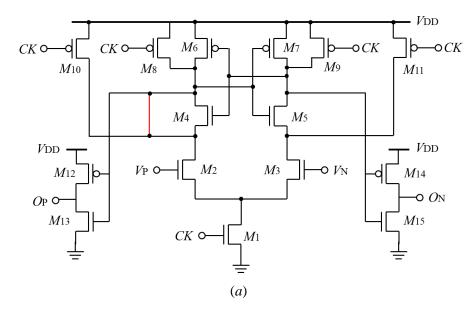

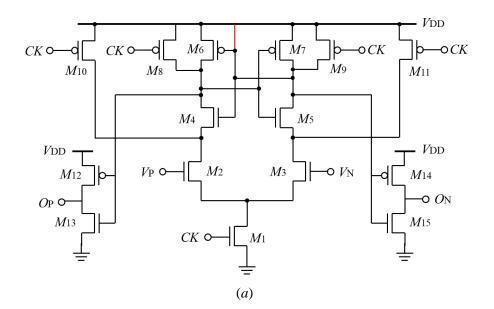

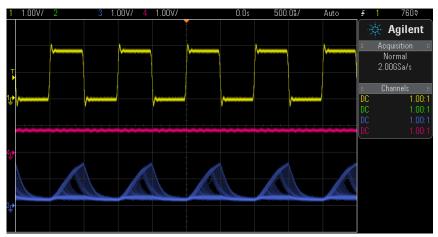

| Figure 3.1 The dynamic comparator in [10]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

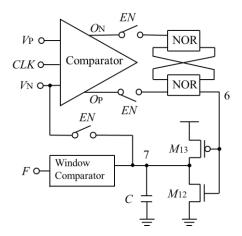

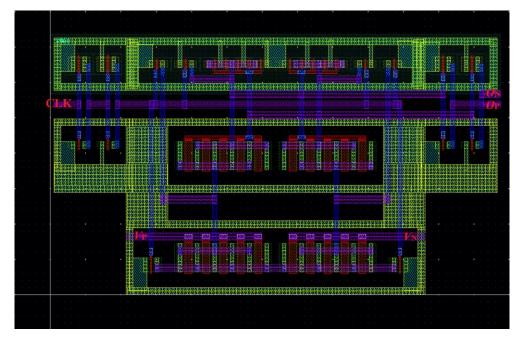

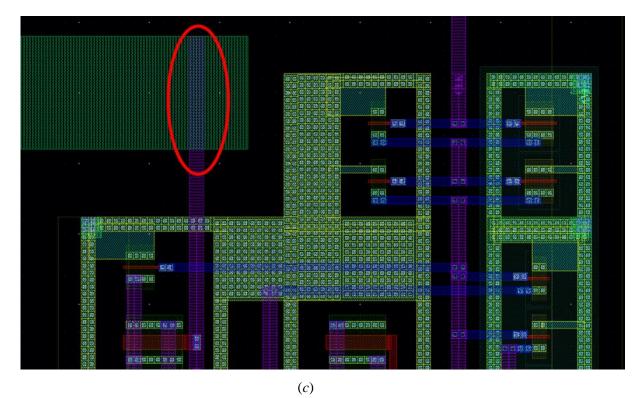

| Figure 3.2 The proposed BIST scheme for dynamic comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

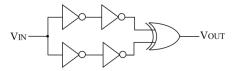

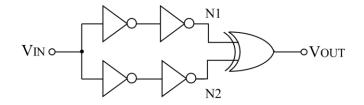

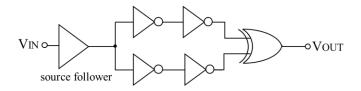

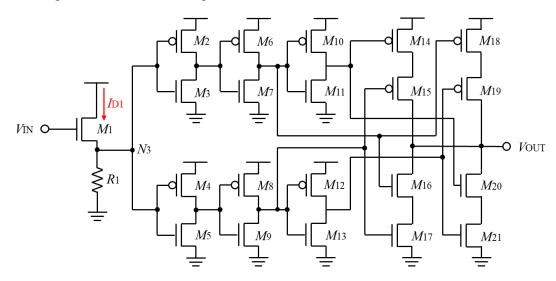

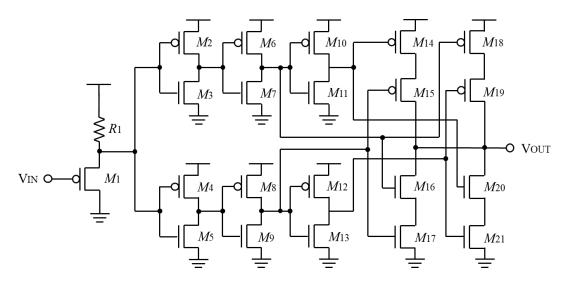

| Figure 3.3 The structure of the window comparator in [11]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

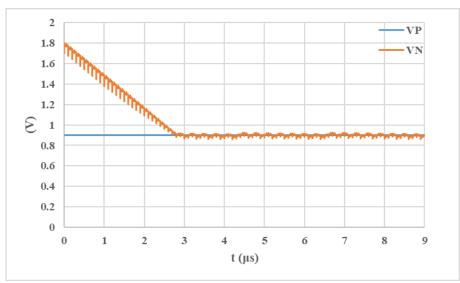

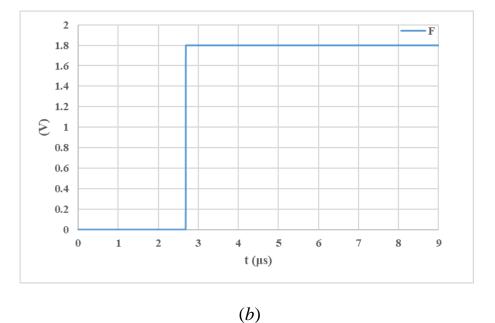

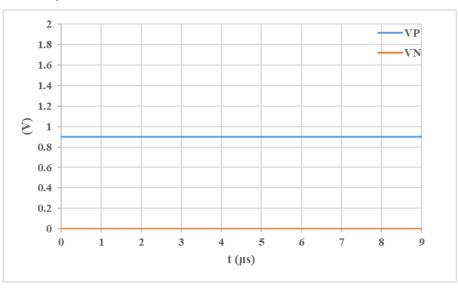

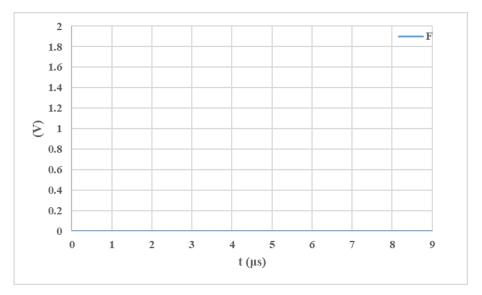

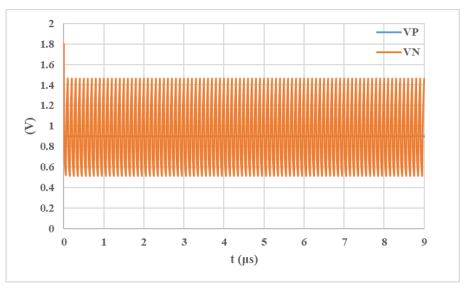

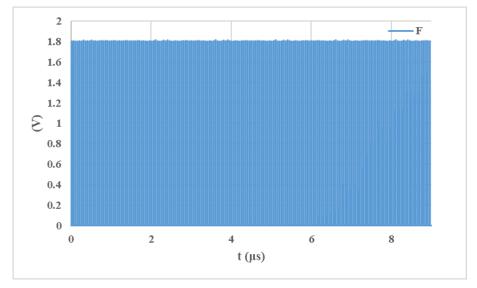

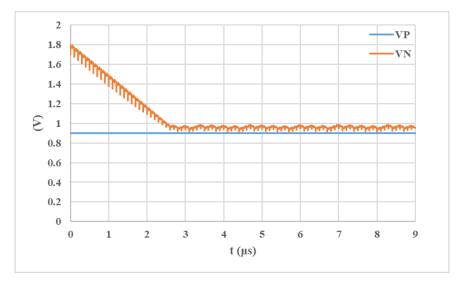

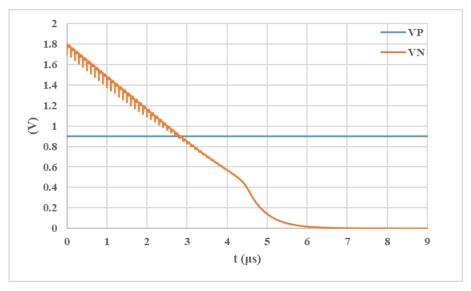

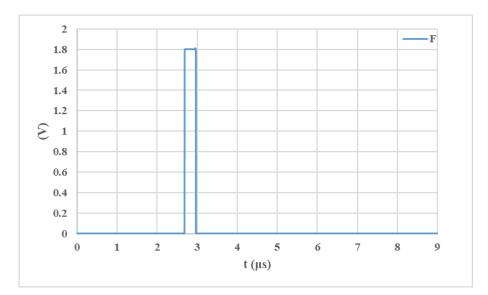

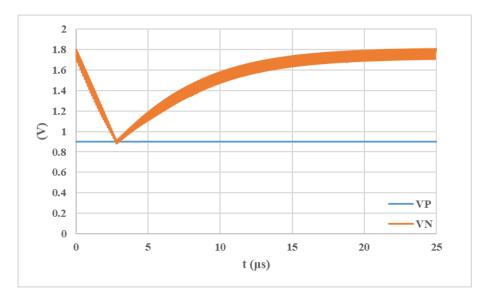

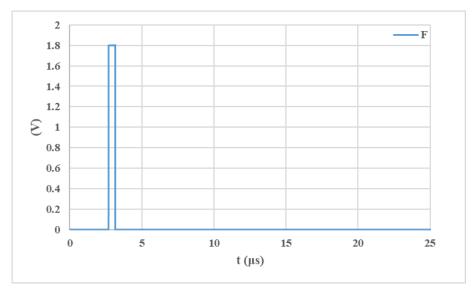

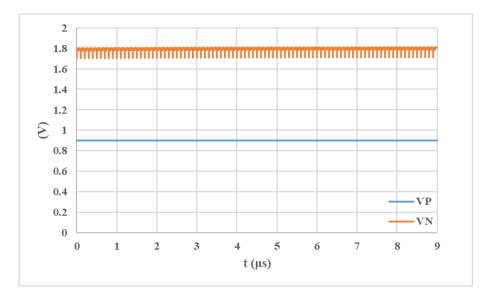

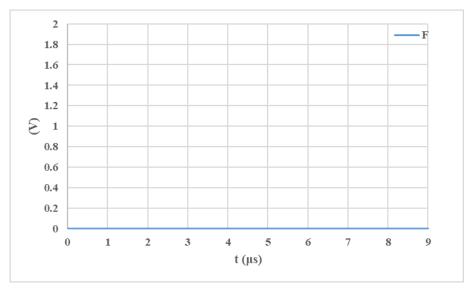

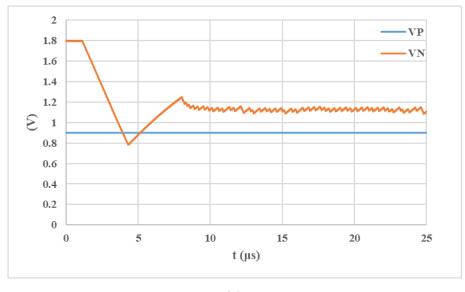

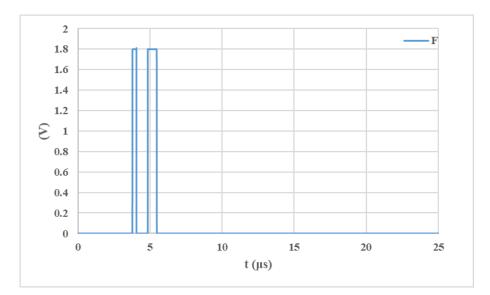

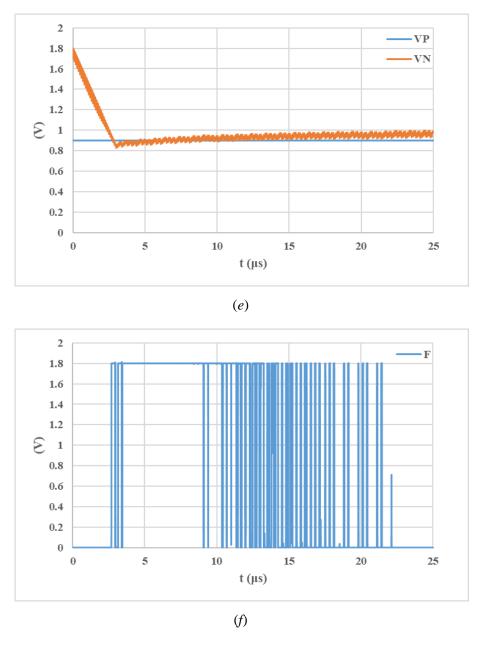

| Figure 3.4 The fault-free simulation result. (a) $V_{\rm P}$ and $V_{\rm N}$ signal (b) F signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

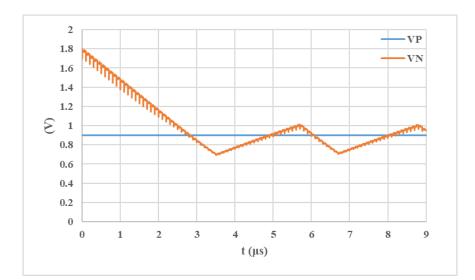

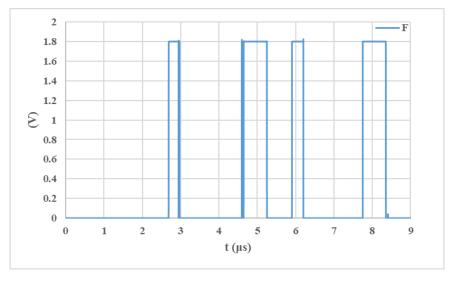

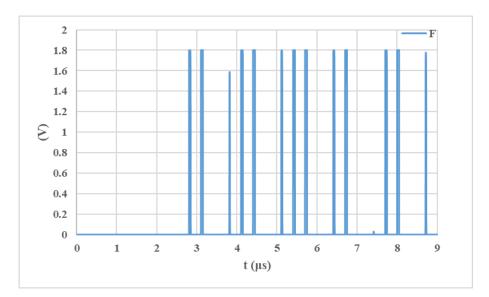

| Figure 3.5 The first fault type. (a) VP and VN signal (b) P signal (b) P signal (b) P signal (c) |

| (b) F signal of faulty circuit with a GDS of M1, (c) VP and VN signal of faulty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| circuit with a GDS of M10, and ( <i>d</i> ) F signal of faulty circuit with a GDS of M10.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

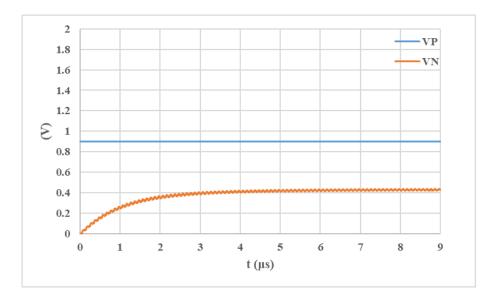

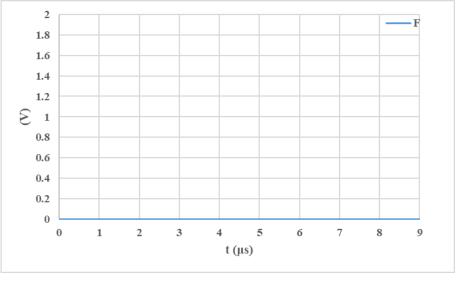

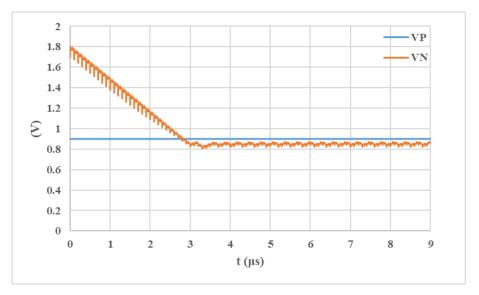

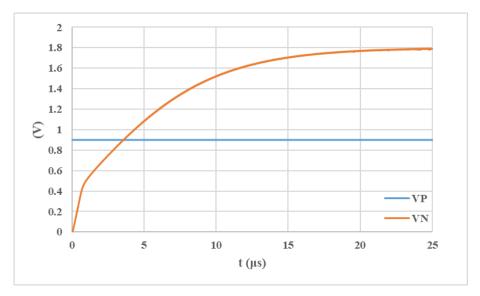

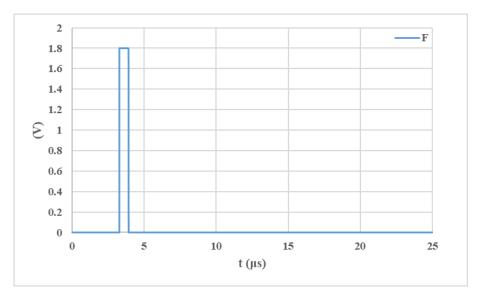

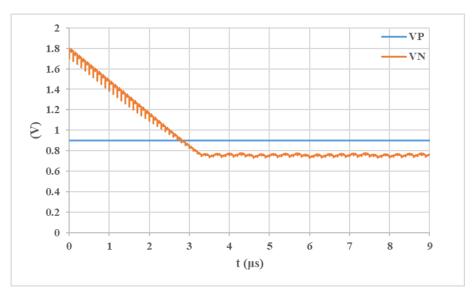

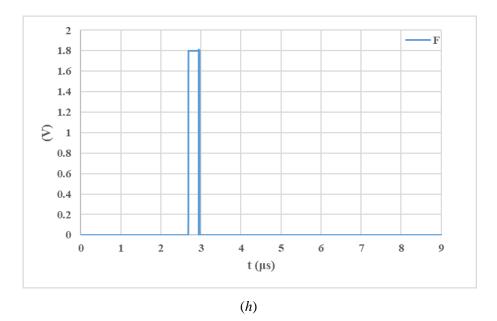

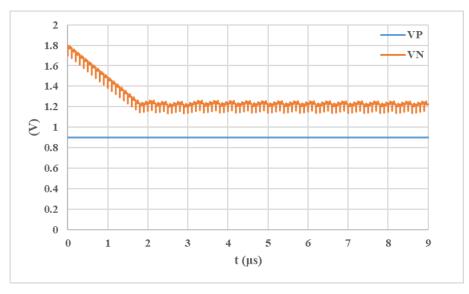

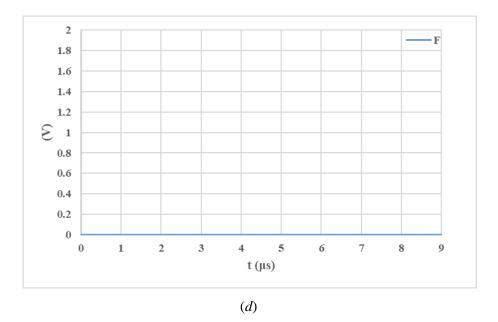

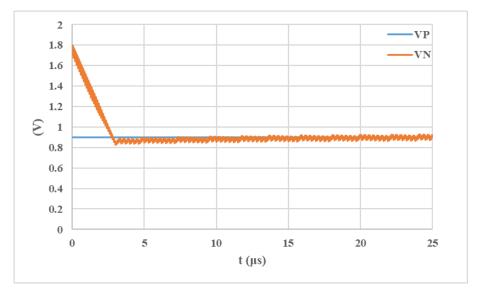

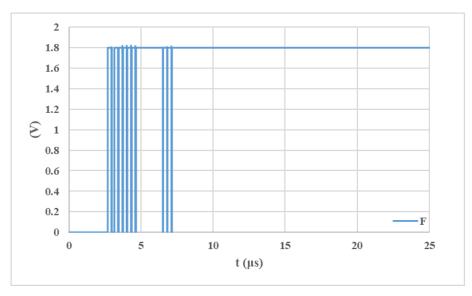

| Figure 3.6 The second fault type. (a) $V_{\rm P}$ and $V_{\rm N}$ signal of faulty circuit with a GDS of $M_2$ ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| (b) F signal of faulty circuit with a GDS of M2, (c) $V_P$ and $V_N$ signal of faulty circuit with a DO of $M_{-}$ (c) $V_{-}$ and $V_{-}$ signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| with a DO of $M_8$ , (d) F signal of faulty circuit with a DO of $M_8$ , (e) $V_P$ and $V_N$ signal of faulty circuit with a DO of $M_{-1}$ (c)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| of faulty circuit with a DO of $M_{11}$ , (f) F signal of faulty circuit with a DO of $M_{11}$ , (g)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| $V_{\rm P}$ and $V_{\rm N}$ signal of faulty circuit with an SO of $M_6$ , And (h) F signal of faulty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| circuit with an SO of $M_6$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

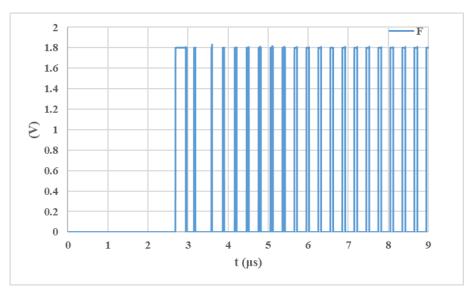

| Figure 3.7 The third fault type. (a) $V_{\rm P}$ and $V_{\rm N}$ signal of faulty circuit with a GDS of $M_3$ ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| (b) F signal of faulty circuit with a GDS of $M_3$ , (c) $V_P$ and $V_N$ signal of faulty circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| with a GDS of $M_8$ , (d) F signal of faulty circuit with a GDS of $M_8$ , (e) $V_P$ and $V_N$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| signal of faulty circuit with a DSS of $M_{13}$ , (f) F signal of faulty circuit with a DSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| of $M_{13}$ , (g) $V_P$ and $V_N$ signal of faulty circuit with a DSS of $M_4$ , and (h) F signal of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| faulty circuit with a DSS of $M_4$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 3.8 The fourth fault type. (a) $V_P$ and $V_N$ signal of faulty circuit with a GDS of $M_{14}$ ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

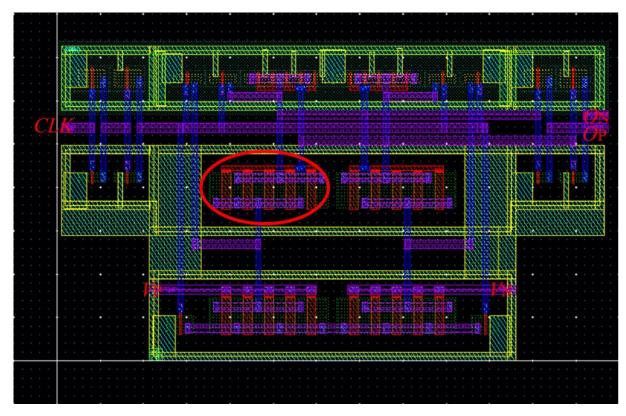

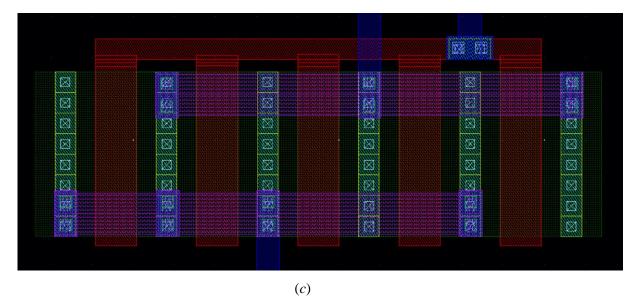

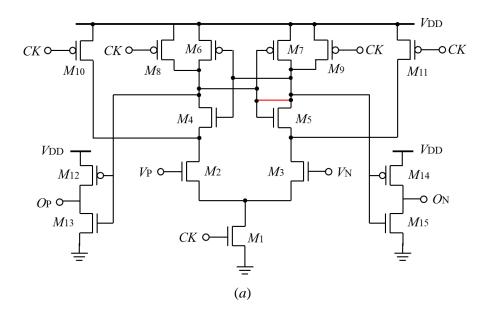

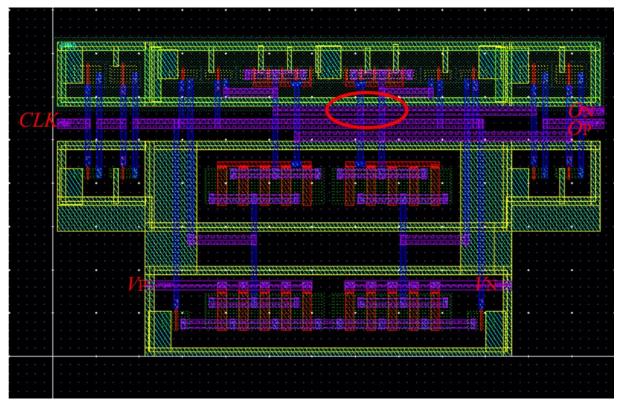

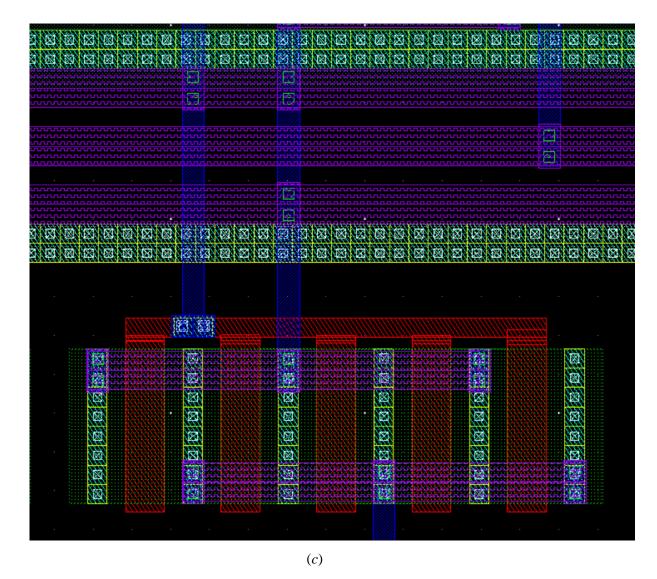

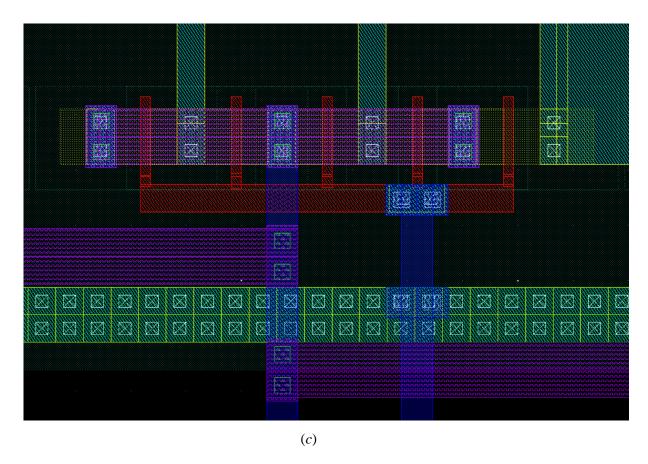

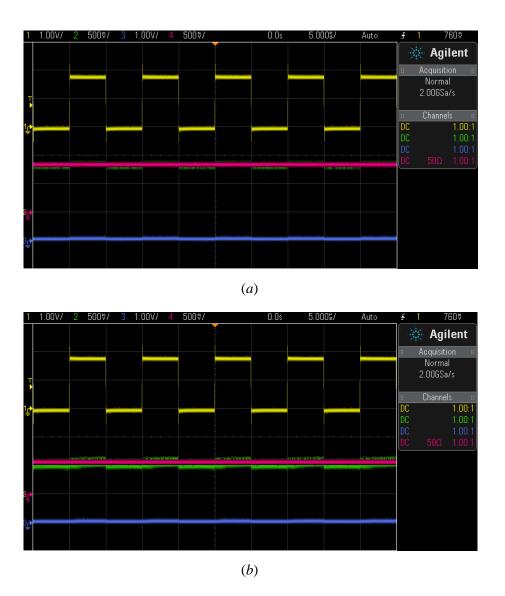

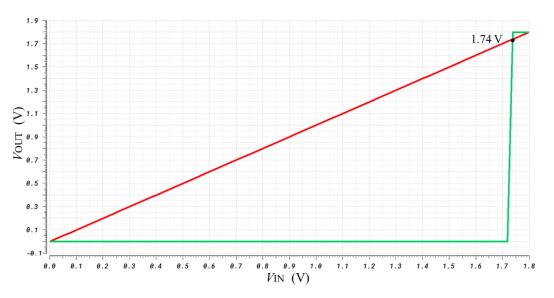

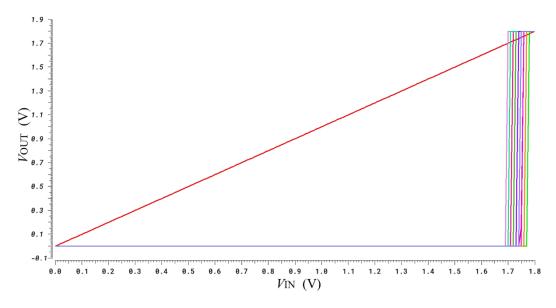

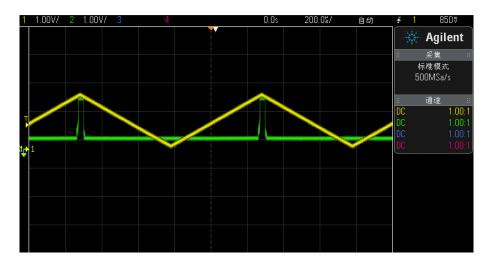

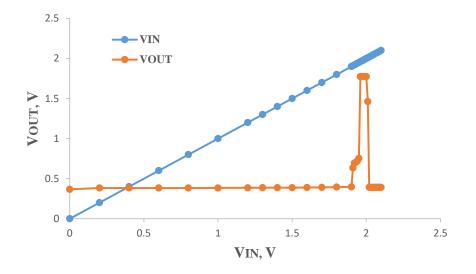

| (b) F signal of faulty circuit with a GDS of $M_{14}$ , (c) $V_P$ and $V_N$ signal of faulty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |