# 修士論文

### 仮想環境を用いた SRAM 型 FPGA における ソフトエラー評価手法

Evaluation Method of System-level Soft Error on SRAM based FPGA Using Virtual Environment

### 報告者

学籍番号: 1245058 氏名: 田中 知成

### 指導教員

密山 幸男 教授

令和4年2月18日

高知工科大学大学院工学研究科 基盤工学専攻電子・光工学コース

# 目次

| 第1章   | 序論                         | 1  |

|-------|----------------------------|----|

| 第 2 章 | SRAM 型 FPGA におけるソフトエラー     | 4  |

| 2.1   | SRAM 型 FPGA                | 4  |

| 2.2   | <b>FPGA</b> におけるソフトエラー     | 7  |

| 2.3   | <b>FPGA</b> におけるソフトエラー評価手法 | 8  |

|       | 2.3.1 エラー挿入実験              | 9  |

|       | 2.3.2 中性子照射実験              | 9  |

| 第3章   | 仮想環境を用いた評価手法               | 11 |

| 3.1   | 提案評価環境の全体構成                | 11 |

| 3.2   | 自動運転システム                   | 11 |

| 3.3   | 仮想環境を用いたソフトエラー評価           | 13 |

| 3.4   | ソフトエラーの観測                  | 14 |

|       | 3.4.1 ソフトエラーの分類            | 14 |

|       | 3.4.2 ビットアップセットの検出         | 14 |

|       | 3.4.3 SEFI の検出             | 16 |

|       | 3.4.4 深刻な誤動作の検出            | 17 |

| 第 4 章 | エラー挿入実験                    | 19 |

| 4.1   | 実験方法                       | 19 |

| 4.2   | 実験結果                       | 20 |

| 第 5 章 | 中性子照射実験                    | 25 |

| 5.1   | 実験方法                       | 25 |

| 5.2   | 実験結果                       | 27 |

| 第6章   | ソフトエラー率の分析                 | 29 |

| 6.1   | エラー挿入実験と中性子照射実験の結果の比較      | 29 |

| 6.2   | エラー訂正回路                    | 30 |

| 第7章   | まとめ                        | 34 |

| 謝辞    |                            | 35 |

参考文献 36

# 第1章 序論

プロセスの微細化に伴い半導体集積回路 (LSI:Large Scale Integrated circuit) では、ソフトエラーの懸念が高まっている。ソフトエラーは放射線が原因で生じる半導体素子内の一過性のエラーであり、Static Random Access Memory (SRAM) や Flip-Flop (FF) のデータの反転などを引き起こす。ソフトエラーによる半導体デバイスの故障は、以前は主に放射線が多い宇宙環境における問題であった。しかし、近年のトランジスタの微細化によって、システムおよびデバイス全体におけるソフトエラーの発生率が高くなっており [1]、地上のデバイスでもソフトエラーの影響が顕在化してきた [2, 3, 4, 5]。特に、誤動作が人命に関わるような自動車や医療機器においては、ソフトエラーの影響が致命的な事故に繋がる可能性が高い [6, 7]。

自動車産業では、ISO26262 [8] で定める自動車のハードウェアおよびソフトウェアの品質 試験に、ソフトエラーが原因で発生すると考えられる故障に対する耐性試験を含んでいる。今後の自動運転技術の発展に伴い、システムが人命保護の役割を担うようになると、自動車 における信頼性はさらに重要な問題になる [9]。システムが運転動作の全てを担うような高いレベルの自動運転では、Light Detection And Ranging (LiDAR) やミリ波レーダ等のセンサに加えて、カメラを用いた画像処理による車体周辺環境の認識も重要になると考えられる [10]。Feild Programmable Gate Array (FPGA) は、並列処理によって高速な画像処理を実現できることから、リアルタイムの処理速度を要求される自動運転アプリケーションでの使用も期待されている [11, 12, 13]。そのため、将来の自動運転の実現に向けて、FPGA におけるソフトエラーの評価は非常に重要である。

近年、回路の構成情報を SRAM に格納する SRAM 型 FPGA は広く普及している。回路構成情報の格納に使用される SRAM は、Configuration RAM (CRAM) と呼ばれる。SRAM および CRAM はソフトエラーの影響を受けやすいことが課題となっている [14, 15]。ソフトエラーによってビットの値が反転する現象はビットアップセット呼ばれる。システムの構成にとって重要な CRAM ビットでビットアップセットが発生すると、FPGA の論理機能の故障が引き起こされる。これらは、Single Event Fucntional Interrupt (SEFI) として定義され、基本的には FPGA を再構成するまで解消されない。FPGA は CRAM の他にも Block RAM (BRAM) やフリップフロップ (FF:Flip Flop) といったメモリ要素を含んでおり、FPGA におけるビットアップセットについて多数報告されている。Xilinx 社は、FPGA のメモリ要素におけるビットアップセットの発生確率を照射実験によって評価している [16]。さらに詳細な研究として、1 つの粒子によってメモリの複数のビットが反転する現象の発生パターンの分析なども行われている [17]。また、放射線の種類や放射線のエネルギーとビットアップセットの発生率の関係に着目した評価も行われている [18, 19, 20]。

さらに、FPGA に実装されたアプリケーションにおける信頼性の評価として、CRAM の ビットアップセット起因の SEFI に着目した研究も多く報告されている。ソフトコアプロ セッサや行列乗算など一般的に広く使用されるアプリケーションにおける評価は非常に多 くの文献で評価されている [21, 22, 23, 24, 25]。また、FPGA に実装した自動運転向け画像 処理アプリケーションの評価も行われている [26, 27, 28, 29, 30, 31, 32]。なかでも畳み込 みニューラルネットワーク (CNN:Convolutional Neural Network) は最もよく用いられる機 械学習アルゴリズムのひとつであり、人工的にソフトエラーの発生を再現するエラー挿入 実験 [26] と照射実験 [27, 28, 29, 30] によって評価されている。CNN の各レイヤの SEFI の分析 [28] や、量子化を適用した CNN と Triple Modular Redundancy (TMR) を適用した CNN の信頼性分析 [29] などが行われている。CNN で使用するデータ型と信頼性の関係は 文献 [30] で評価されている。また、単純な画像処理フィルタであるメジアンフィルタやガ ウシアンフィルタなどにおける信頼性は、エラー挿入実験によって評価されている[31,32]。 一方で、これらの文献におけるアプリケーションの SEFI は、FPGA の論理機能の故障と してのみ定義されており、FPGA の論理機能の故障が自動運転システムに対して及ぼす影響 についてまでは評価されていない。すべての FPGA の論理機能の故障が自動運転システム に対して一様な影響を及ぼすとは限らないため、自動運転システム全体における影響を評価 することは非常に重要であると考える。FPGA の論理機能の故障が自動運転における誤った 運転操作を引き起こし、またこれが繰り返される場合には、自動運転システムにとって致命 的な故障となる。

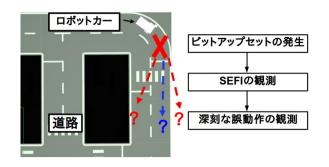

そこで本研究では、FPGAに実装した複数の画像処理フィルタと車線検出に基づいて走行を行う自動運転システムを対象に、CRAMのビットアップセットによる影響を評価する。3Dシミュレータ Gazebo [33] によって提供される仮想環境に道路環境を構築し、仮想環境上でロボットの自動運転を実施する。仮想環境上で自動運転ロボットの挙動を監視することで、自動運転システムに発生する SEFI のうち、深刻な誤動作とそうでないものを分類する [34]。CRAM で発生したビットアップセットが画像処理アプリケーションの誤ったデータの転送などを引き起こした場合に、SEFI の発生とみなす。SEFI が最終的に Gazebo 上の自動運転ロボットの脱線を引き起こした場合に、その SEFI を深刻な誤動作として分類する。提案する評価環境を用いて照射実験とエラー挿入実験の両方を行い、CRAM で発生したビットアップセットと SEFI および深刻な誤動作の関係を明らかにすることを目指す。また、照射実験の結果とエラー挿入実験の結果を比較することで、提案する仮想環境を用いたソフトエラー評価手法の妥当性を検証する。

本論文は全7章で構成する。第2章では、評価対象として採用した Xilinx 社の FPGA について述べる。また、FPGA におけるソフトエラーの種類とその定義を説明したうえで、FPGA におけるソフトエラーを評価するための実験について述べる。第3章では、仮想環境を用いた自動運転システムにおけるソフトエラーの評価手法について述べる。3D シミュレータによる仮想環境と FPGA に実装した自動運転システムを連携させることによる提案

評価環境について述べる。また、自動運転システムにおけるソフトエラーの分類とそれらの観測方法について述べる。第4章では、人工的にソフトエラーを再現するエラー挿入実験による評価について述べる。第5章では、実際に中性子を FPGA ボードに対して照射する中性子照射実験による評価について述べる。第6章では、ソフトエラー率の分析について述べる。エラー挿入実験と中性子照射実験の結果をソフトエラー率の観点で比較し、提案する仮想環境を用いたソフトエラー評価手法の妥当性を検討する。また、エラー訂正回路の有効性の検証について述べる。第7章では、本研究のまとめについて述べる。

# 第2章 SRAM 型 FPGA におけるソフト エラー

本章では評価対象として採用した Xilinx 社の SRAM 型 FPGA について述べる。評価対象の SRAM 型 FPGA はプロセッサを搭載している。自動車や医療機器などのリアルタイム処理や高い信頼性が求められるアプリケーションへの応用に適しているとされているため、評価対象のデバイスとして採用した。また、FPGA におけるソフトエラーの種類とそれらの定義について述べる。FPGA におけるソフトエラーを評価するための実験として、エラー挿入実験と照射実験の概要とそれぞれの特徴について述べる。

#### 2.1 SRAM 型 FPGA

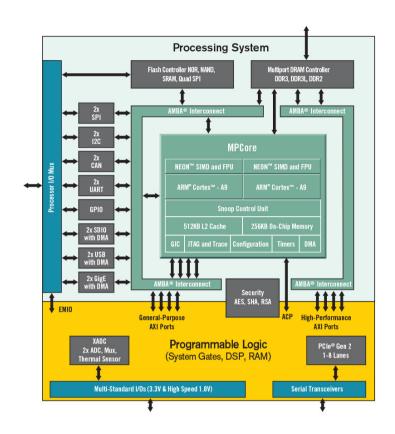

FPGA はユーザの用途に合わせて回路構成を書き換え可能な論理デバイスである。近年、FPGA は広い用途で使用されるようになり、ARM などのハードコアプロセッサを搭載した System-on-a-Chip (SoC) 指向の FPGA が普及している。これらはプログラマブル SoC と呼ばれる。Xilinx 社のプログラマブル SoC は、主に、Processing System (PS) と本質的な FPGA である Programmable Logic (PL) によって構成され、PL と PS 間には複数のインターフェースが用意されている。

評価対象のデバイスとして Digilent 社の FPGA ボード Zybo Z7-20 に搭載される Zynq-7000 All Programmable SoC (APSoC) Z7020 XC7Z020-1CLG400C を採用した。Zynq-7000 Z7020 のブロック図を図 2.1 に示す。PS には、デュアルコア ARM Cortex-A9 プロセッサ、浮動小数点ユニット (FPU:Floating Point Unit)、メモリ管理ユニット (MMU:Memory Management Unit) が搭載されている。また、外部メモリインターフェイスや、各種入出力インターフェイスコントローラがハードマクロ化されており、オンチップインターコネクトの規格である Advanced Microcontroller Bus Architecture (AMBA) プロトコルに基づくスイッチによりプロセッサと接続されている [35]。PS と PL 間の通信には複数のインターフェースが用意されており、高スループットデータ転送に使用される Advanced eXtensible Interface (AXI) ポートや Accelerator Coherency Port (ACP) インターフェイスなどがある。

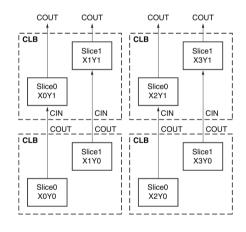

PL は、Xilinx 社 7 シリーズ FPGA Artix-7 と同じ構成になっており、28nm プロセスを採用している。PL には主に、Block RAM (BRAM)、コンフィギューションロジックブロック (CLB:Configurable Logic Block)、デジタルシグナルプロセッサ (DSP:Digital Signal Processor) などのハードウェアリソースがある。これらの構成情報をすべて含んだビットストリームファイルを CRAM に書き込むことによって、ユーザ回路を実装することができる。Xilinx 社 7 シリーズ FPGA の CLB の構成を図 2.2 に示す。1 つの CLB は、直接に相互接

図 2.1 Zynq-7000 Z7020 ブロック図 [36]

図 2.2 7 シリーズ FPGA における CLB の構成 [37]

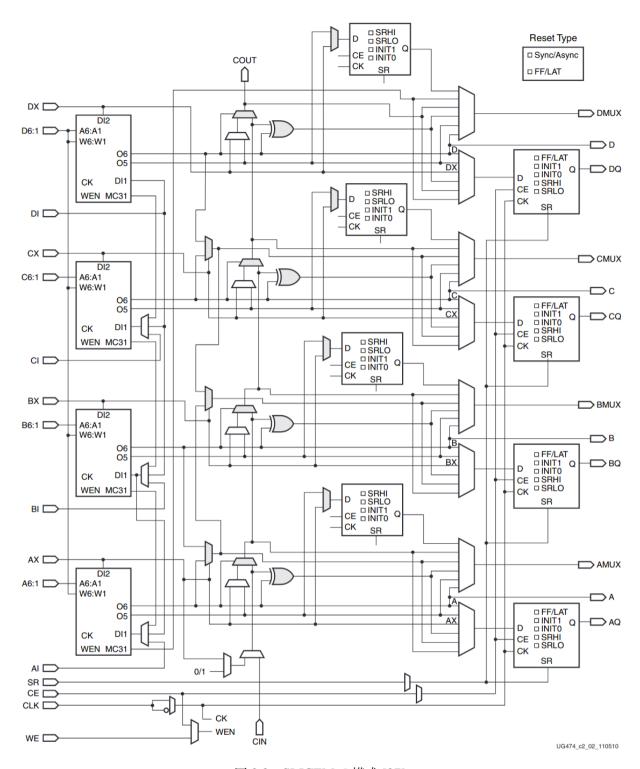

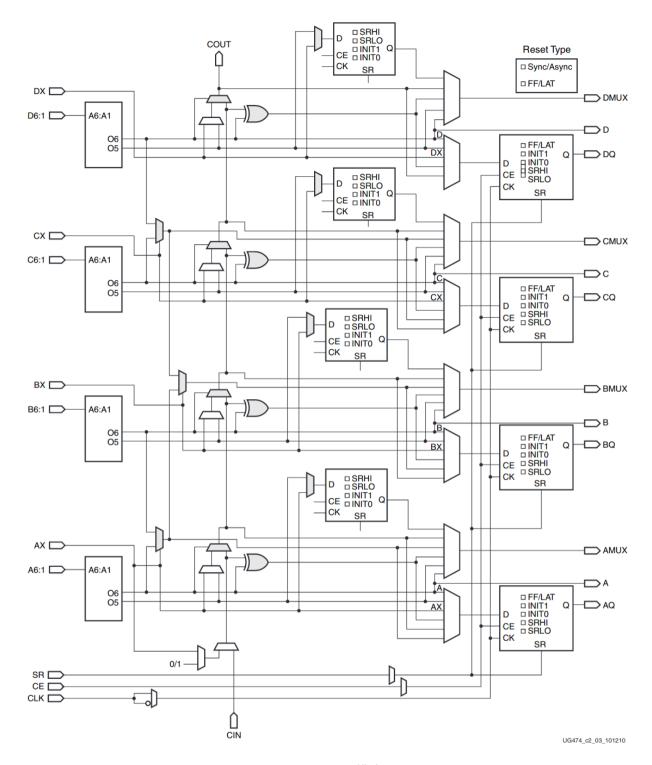

続されていない 2 つのスライスによって構成される。スライスには SLICEM と SLICEL の 2 種類があり、各 CLB には 2 つの SLICEL もしくは、1 つの SLICEL と 1 つの SLICEM が 含まれる。SLICEM と SLICEL の構成を図 2.3 と図 2.4 にそれぞれ示す。両者のスライス は、4 つの 6 入力 Lookup Table (LUT)、8 つのストレージエレメント、多入力機能マルチプレクサ、キャリーロジックを含んでおり、ロジックファンクション、演算機能、Read Only Memory (ROM) 機能を実現することができる。これらに加えて、SLICEM は分散 RAM に よるデータ格納と 32 ビットレジスタを使用したデータシフトの機能をサポートしている。

図 2.3 SLICEM の構成 [37]

図 2.4 SLICEL の構成 [37]

### 2.2 FPGA におけるソフトエラー

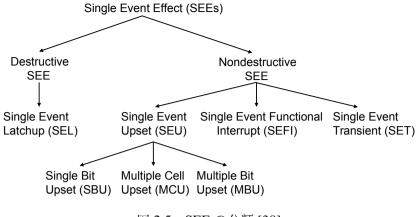

Single Event Effect (SEE) は、1 つの粒子によって引き起こされる電子デバイスの故障である。SEE は、荷電粒子が電子デバイス中のシリコン原子と反応することによって生じる。 SEE の分類を図 2.5 に示す。SEE は、大きく Disructive SEE と Nondisructive SEE に分

図 2.5 SEE の分類 [38]

けられる。Disructive SEE は、ハードエラーであり、ハードウェアの恒久的な故障とし て分類される。Single Event Latchup (SEL) は、放射線により LSI に寄生するサイリスタ が ON 状態となることで大きな電流が流れる現象である。SEL は再起動で直る場合もあ るが、永久的な故障を引きこすことがあるため Disructive SEE として分類される。一方、 Nondisructive SEE は、ハードエラーではない一時的な故障として定義され、保持データの破 壊や、誤った計算結果の出力などが含まれる。Nondisructive SEE は本質的にソフトエラー である。Nondisructive SEE は、Single Event Transient (SET)、Single Event Upset (SEU)、 Single Event Functional Interrupt (SEFI) に分類される。SET は放射線の影響により組み合わ せ回路の論理ゲートの出力が反転する現象である。論理ゲートの入力の値は影響を受けてい ないため、論理ゲートの誤った出力は、一定時間後に正常に戻る。論理ゲートの誤った出 力値がもとに戻るまでの時間幅のパルスが SET である。SEU は放射線の影響によりメモリ や FF などの記憶素子の値が反転する現象である。一般的に SEU はソフトエラーと呼ばれ ることが多い。SEU が発生して、ビットが反転する現象はビットアップセットと呼ばれる。 ビットアップセットには、Single Bit Upset (SBU)、Multiple Cells Upset (MCU)、Multiple Bit Upset (MBU) が含まれる。SBU は、1 つのビットが反転する現象であり、MCU/MBU は 複数のビットが反転する現象である。ここで、MCU は複数ワードに渡って発生する複数の SBU として定義され、MBU は同一ワード内で発生する複数のビット反転として定義され る。SEFI は放射線の影響により、FPGA の論理機能の故障が引き起こされる現象である。

### 2.3 FPGA におけるソフトエラー評価手法

FPGAのCRAMを対象としたソフトエラーの評価実験について述べる。意図的にCRAMにエラーを挿入してソフトエラーの発生を再現するエラー挿入実験と、実際に中性子を評価対象ボードに照射する中性子照射実験について、それぞれの概要と特徴を述べる。

#### 2.3.1 エラー挿入実験

CRAM に意図的にエラーを挿入することでソフトエラーの発生を再現する [39, 40]。 CRAM は、フレーム、ワード、ビットといった単位で細分化される。フレームとワードは、CRAM のビットのまとまりを表す単位であり、1フレームは複数のワード、1ワードは複数のビットによって構成される。1フレームあたりのワード数および1ワードあたりのビット数は FPGA によって異なる。このような CRAM の構成上、フレームアドレス、ワードアドレス、ビットアドレスの3つのアドレスを指定することで CRAM ビットを特定することができる。エラーの挿入は、任意の CRAM ビットの値を人工的に反転させることを意味する。SBU を評価対象とした場合、任意の1ビットを反転させるエラー挿入を行った後、反転したビットがシステムにどのような影響を及ぼすか観測する [41]。1回の実験が終了すると、反転させたビットを元の状態に戻し、別のビットに対するエラー挿入を行う。エラー挿入対象の CRAM ビットの数が膨大で、すべてのビットに対してエラー挿入を行うことは非常に時間がかかる場合が多い。一般にこのような問題を解決するために、ランダムにサンプリングした CRAM ビットに対してエラー挿入を行う手法が用いられる [42, 43]。

エラー挿入実験の利点は、比較的簡単に実験を実施できることである。人工的にソフトエラーを再現するため、ソフトエラーの発生を待つ必要がないうえに、大掛かりな実験用デバイスのセットアップの必要がない。そのため、短時間で多くのビット反転の影響を観測できる [44]。エラー挿入対象の CRAM ビットが多い場合には長時間を要するが、次々にエラー挿入対象のビットを変えながら連続して実験を行うことができることから、効率的に多くのビット反転の影響を観測可能である [45, 46, 47]。また、エラー挿入実験では、実験対象でないメモリのエラーは発生しないため、観測された SEFI は確実に人工的に発生させた CRAMのビット反転によって引き起こされたものであると言える。エラー挿入のタイミングやエラー挿入を行うビットなどの条件は比較的容易に変えることができるため、様々なビットアップセットを想定して影響を分析することも可能である [48]。

#### 2.3.2 中性子照射実験

エラー挿入実験よりも高い精度で、ソフトエラーの影響を評価するために中性子照射実験を行う [49,50]。中性子ビームは加速した陽子を用いて生成される。中性子ビームのライン上に評価対象の FPGA ボードを設置することで、地上よりもはるかに多くの数のビットアップセットを観測することができる。実際に評価対象の FPGA ボードに対して中性子を照射するため、実環境で発生するソフトエラーの影響を非常に高い精度で評価することができる。このような特徴から中性子照射実験は、エラー挿入実験の結果の妥当性を評価するために行われることもある [51,52]。

SEU のビットアップセットの影響を評価する際は、CRAM におけるビットアップセッ

トが検出された後、ビットアップセットに起因した SEFI が発生するかどうかを観測する。 ビットアップセットの累積の影響を避けるために、SEFI の発生を一定時間観測した後、 FPGA を再構成して次のビットアップセットの発生を待つ。これを繰り返して行うことで、 ビットアップセットと SEFI の関係を評価することができる。

中性子照射実験は評価精度が高い一方で、実験施設やマシンタイムに限りがあり、実験費用が高いデメリットがある。ビットアップセットが発生するタイミングやビットアップセットが発生する箇所は事前に予測することはできないため、数多くのビットアップセットの影響を効率的に評価することは、エラー挿入実験に比べて非常に難しい。また、発生するビットアップセットには、SBUだけでなくMBU/MCUも含まれるため、実験結果の分析ではこれらの影響を考慮する必要がある。また、中性子照射実験の間、基本的に中性子ビームは止まることがないため、意図しないビットアップセットの累積や、評価対象以外のメモリでのビットアップセットなどの影響も考慮する必要がある。さらに、中性子ビーム下の評価デバイスの予期しない故障や、ログデータの取り扱い等に注意する必要がある。中性子ビームの照射中、実験室内には入ることができないため、コンクリート壁で隔てられた実験室外からの評価デバイスとの通信や、評価デバイスの電源制御など実験時には工夫が必要である。

# 第3章 仮想環境を用いた評価手法

FPGA に実装した自動運転システムと 3D シミュレータ Gazebo を連携することで実現する提案評価環境の全体構成について述べる。仮想環境上で自動運転ロボットの挙動を監視することで、自動運転システムにおける SEFI のうち、自動運転ロボットの決められた道路範囲からの脱線を引き起こす SEFI を深刻な誤動作として分類する。評価対象の自動運転システムの定義と自動運転システムにおけるソフトエラーの分類について説明した上で、それらの観測方法について述べる。

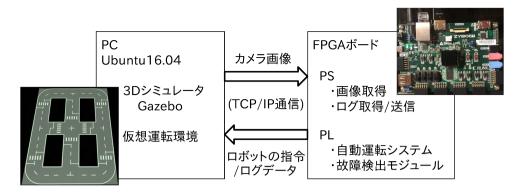

### 3.1 提案評価環境の全体構成

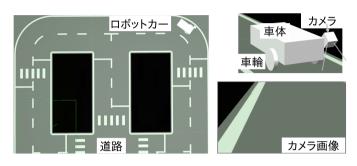

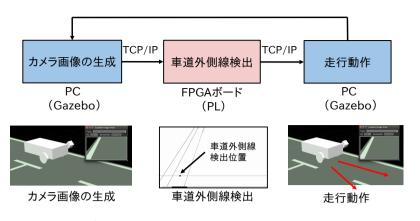

3D シミュレータによる仮想環境と自動運転システムを実装した FPGA を連携させるこ とで、自動運転システムにおける SEFI のうち、自動運転ロボットの決められた道路範囲か らの脱線を引き起こす重大な SEFI を深刻な誤動作として分類する。提案するソフトエラー 評価環境の全体構成を図 3.1 に示す。提案評価環境は 1 台の PC と 1 台の FPGA ボードに よって構成される。Ubuntu OS を搭載した PC では、オープンソースのロボットシミュレー タ Gazebo を用いて、仮想運転環境を構築した。仮想運転環境には、自動運転ロボットと 道路環境が含まれる。Gazebo は、カメラ画像の生成、自動運転ロボットに対する指令の受 信、自動運転ロボットの走行動作の実行を担う。FPGA の PS では主に PC とのデータのや り取りを行う。PL に実装した自動運転システムは、画像処理によって車道外側線検出を行 う。また、PL には CRAM のビットアップセットの検出と DUT の状態監視を行うための故 障検出モジュールを実装した。故障検出モジュールのログデータは、自動運転ロボットへの 指令と一緒に PC 側に転送される。 PC と FPGA 間の通信は、大きな遅延の発生を避けるた め、高速な通信が可能な Transmission Control Protocol (TCP/IP) 通信を採用した。図 3.2 に Gazebo を使用して構築した仮想運転環境を示す。道路環境として、International Conference on Feild Programmable Technology (ICFPT) 2019 で開催された FPGA デザインコンテスト で使用されたコースを採用した。また、自動運転ロボットとして、前方に2つの車輪を取り 付け、車体左側にカメラを取り付けたシンプルなモデルを作成した。カメラからは解像度 640×480の画像を取得する。

### 3.2 自動運転システム

カメラ画像をもとに決められた道路範囲を車道外側線に沿って走行するレーンキープ制御を自動運転システムとして定義する。自動運転システムの画像処理はすべて Zynq-7000の PL に実装しており、評価実験における Design Under Test (DUT) とする。車道外側線に

図 3.1 提案するソフトエラー評価環境の構成

図 3.2 3D シミュレータ Gazebo によって構築した仮想運転環境

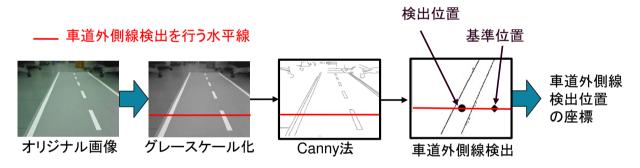

図 3.3 Canny 法によるエッジ検出画像を用いた車道外側線検出

沿ってレーンキープ制御を行うために、DUT は入力されたカメラ画像から車道外側線の検 出を行う。車道外側線検出のための処理については先行研究 [53] で詳しく述べている。

図 3.3 に車道外側線検出のための画像処理フローを示す。Canny 法を用いて、画像内のエッジラインの検出を行う [54]。その後、図 3.3 の水平方向の赤色の線上で、車道外側線の検出を行う。車道外側線の検出位置と基準位置の差があらかじめ決めた値を保つように進行方向を決定する。進行方向は、直進、左進行、右進行の 3 つの内のいずれかである。

DUT の構成は、図 3.3 に対応しており、グレースケール化、Canny 法、車道外側線検出の 3 つのモジュールによって構成される。これら 3 つのモジュールは全て Xilinx 社 Vivado HLS を用いて作成した。また、自動運転システムは、地上で使用するアプリケーションを想定しているため放射線対策の設計は行なわず、論理合成等は全てツールに任せている。

図 3.4 仮想運転環境における自動運転ロボットの走行

#### 3.3 仮想環境を用いたソフトエラー評価

仮想運転環境おいて自動運転ロボットの走行を行う際の処理の流れを図3.4に示す。 Gazebo で生成されたカメラ画像は、TCP/IP 通信によって FPGA ボードの PS に転送され る。PS が受け取った画像は、Dynamic Random Access Memory (DRAM) に書き込まれ、PL に実装された DUT は Direct Momory Access (DMA) によって画像を取得する。 DUT は、画 像処理によって車道外側線検出を行う。DUT の画像処理が終了すると、PS は自動運転ロ ボットへの指令と DUT 監視モジュールのログデータを PC 上の Gazebo に送信する。その 後、Gazebo は、PS から受け取った自動運転ロボットへの指令に基づいて、自動運転ロボッ トの走行動作を実行する。Gazebo は自動運転ロボットを 1 ミリ秒間走行させた後、自動運 転ロボットを停止させ、次のカメラ画像の生成を行う。これを繰り返し行うことで、仮想運 転環境上での自動運転を実現した。PLの DUT は 100MHz で動作し、画像処理は 60 frames per second (fps) で行うことができる。しかし、PCと FPGA ボード間でのデータ転送に時間 がかかるため、図 3.4 の一連の処理は約 3fps である。評価実験におけるテストランは、最大 700 フレームの画像によって構成される。つまり、図 3.4 の一連の流れを 700 回繰り返すこ とを意味する。1回のテストランが終了すると、PLのすべての回路を確実に故障がない状 態に戻すために、CRAM の全てのデータを書き直す。この際、CRAM のデータを書き直す ことと同時に、仮想運転環境の自動運転ロボットをテストランのスタート位置に戻す。DUT の画像処理に基づいた自動運転ロボットへの指令が送られてくるまでその場で停止させ、自 動運転ロボットへの指令の受信と同時に走行を開始させる。評価実験において、CRAM で ビットアップセットが発生した際は、ビットアップセットの発生後で200フレームの画像処 理が行われる間、FPGA の回路の動作と自動運転ロボットの挙動を監視する。

図 3.5 FPGA に実装した自動運転システムにおけるソフトエラーの分類

#### 3.4 ソフトエラーの観測

評価実験では、CRAM におけるビットアップセットが自動運転システムに対してどのような影響を与えるか評価を行う。本節では、自動運転システムにおけるソフトエラーの分類と、それらの観測方法について述べる。

#### 3.4.1 ソフトエラーの分類

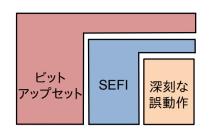

FPGAの CRAM をソフトエラー評価の対象とする。ソフトエラーのレベルをビットアップセット、SEFI、深刻な誤動作の3つで定義した。これらの関係を図3.5に示す。図3.5で、ビットアップセットは CRAM における SBU、MCU、MBU を含んでいる。ここで、MCUは複数ワードに渡って発生する複数のSBUであり、MBUは同一ワード内で発生する複数のビット反転として定義する。ビットアップセットが発生しても、必ずしも SEFI が引き起こされるとは限らない。回路の動作上、反転したビットが参照されない場合もあるからである。反転したビットが回路の動作に関わるビットであった場合にのみ SEFI が観測される。そこで、SEFIは、FPGAの論理機能の故障として定義する。例えば、SEFIにはモジュールの計算結果の誤りなどが含まれる。全ての SEFI はゴールデン出力との比較によって判断する。また、SEFIの中で、最終的にシステムに対して大きな影響を及ぼし自動運転ロボットの決められた道路範囲からの脱線を引き起こす SEFI を深刻な誤動作として定義する。仮想環境上で自動運転ロボットの挙動を監視することで、自動運転ロボットの脱線を判定する。

#### 3.4.2 ビットアップセットの検出

CRAM のビットアップセットを検出するために、Xilinx 社 Soft Error Mitigation (SEM) IP [55] を使用した。SEM IP は、DUT と同じ PL に実装するが、DUT とは独立して動作する。DUT が画像処理を行う間、SEM IP は、1 ワード (32 ビット) ずつ CRAM 内をチェックする [56]。Cyclic Redundancy Check (CRC) に基づいて、1 ビットのエラー訂正と 2 ビットのエラー検出 (SECDED:Single-bit Error Correction Double-bit Error Detection) を行うことができる。今回の設計では、SEM IP は 100MHz で動作する。Zynq-7000 の CRAM

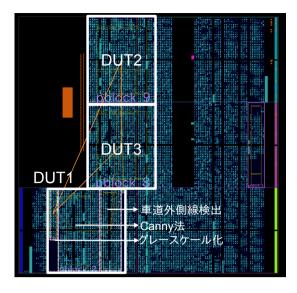

図 3.6 Zyng-7000 における DUT の配置

の 25.7Mbit であれば、約 8 ミリ秒でチェックすることが可能である。また、DUT 内で発生したビットアップセットを DUT 外のビットアップセットと区別するために、Automatic Configuration Memory Error-injection (ACME) [24] を用いて、DUT のビットアドレスの範囲を計算する。DUT のビットアドレスに基づいて、DUT 内で発生したビットアップセットが SEFI を引き起こすかどうか観測する。

より多くのビットアップセットを観測するために、PL内に3つのDUTを実装した。図3.6に Zynq-7000 APSoC XC7Z020-1CLG400CにおけるフロアプランでのDUT配置の様子を示す。DUTのビットアドレスを計算するためのフロアプランとして、1つのDUTを1つの矩形の範囲内に配置している。エラー挿入実験と中性子照射実験の両者とも図3.6の設計を対象に評価を行う。それぞれのDUTを配置する矩形は完全に同じではないが、ロジックはすべてのDUTで同じである。中性子照射実験において各DUTで発生するビットアップセットに偏りが起きないように、DUTを配置する各矩形内でのCRAMの使用率が一定程度になるようように、矩形の大きさを設定している。図3.6の設計では、DUTを配置する各矩形内のCRAM使用率は70%程度である。

表 3.1 に Zynq-7000 における DUT1 のリソース使用量を示す。DUT2 と DUT3 では DUT1 に比べて 4 つ LUT が多く使用されたが、LUT 以外のリソース使用数は全て一致していた。また、DUT 以外に、PC から転送された画像を取得するモジュールや SEFI を観測するための DUT 監視モジュールがある。これらのモジュールはツールによって自動的に配置している。また、DUT を矩形の範囲内に限定して配置することで、DUT の範囲内で MBU/MCU が発生する可能性が高くなることが懸念される。この懸念については、6.1 節でエラー挿入実験と中性子照射実験の結果に基づいた考察として述べる。

表 3.1 Zynq-7000 における DUT1 のリソース使用量

| リソース      | LUTs   | FFs     | Block RAMs | DSPs   |

|-----------|--------|---------|------------|--------|

| 使用可能数     | 53,200 | 106,400 | 140        | 220    |

| グレースケール化  | 347    | 466     | 0.5        | 3      |

| Canny 法   | 2,869  | 3,847   | 5          | 5      |

| 車道外側線検出   | 1,495  | 1,626   | 0.5        | 3      |

| 合計 (DUT1) | 4,711  | 5,939   | 6          | 11     |

| 使用率       | 8.72 % | 5.28 %  | 4.29 %     | 5.00 % |

#### 3.4.3 SEFI の検出

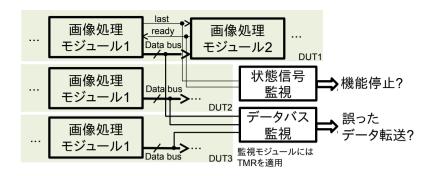

自動運転システムにおける SEFI を観測するために、DUT の監視を行う。DUT の状態を 監視するために、各モジュールの入力信号と出力信号を監視するモジュールを作成した。各 DUT は、グレースケール化モジュール、Canny 法モジュール、車道外側線検出モジュール の3つのモジュールによって構成される。画像データは、AXI Stream のプロトコルによっ て、上流モジュールから下流モジュールに転送される。AXI Stream は主に、モジュールの 状態を表す信号とデータバスによって構成される。

図 3.7 に示すように、DUT 監視モジュールを配置して、モジュールの状態信号とデータバスを監視した。モジュールの状態信号とデータバスの監視において、何らかの異常が観測された場合に SEFI の発生とみなす。まず、モジュールの状態を表す信号として AXI Stream の 'Ready' 信号と 'Last' 信号を監視した。'Ready' 信号は下流モジュールが上流モジュールからデータを受信できる状態であることを示す信号であり、'Last' 信号は上流モジュールが下流のモジュールに対して画像の転送が終了したことを知らせる信号である。1 フレーム分の画像処理が実行される間で、'Ready' 信号もしくは 'Last' 信号が正常に出力されていない場合には、モジュール間の画像データの転送が正常に実行されていないと判断する。そして、その故障をモジュールの機能停止として扱う。次に、3 つの DUT におけるデータバスを各モジュール間で比較しながら監視することで、データ転送の異常を検知する。1 つのDUT が他の DUT と異なるデータを繰り返して出力している場合には、誤ったデータ転送として扱う。DUT 監視モジュールからは、SEFI がどの DUT のどのモジュールで発生したのか区別できる信号を出力している。また、DUT 監視モジュール自体が故障することを避けるために、これらの DUT 監視モジュールはすべて Triple Modular Redundancy (TMR) によって実装している。

図 3.7 DUT 監視モジュールによる DUT の各モジュールの監視

#### 3.4.4 深刻な誤動作の検出

SEFI のうち、特に重大な SEFI である深刻な誤動作を区別するために、仮想環境で自動運転ロボットの挙動を一定時間監視する。一定時間の監視を行う理由として、ビットアップセットが SEFI を引き起こすかどうかは入力画像に依存し、SEFI が自動運転ロボットの挙動に影響を及ぼすかどうかは DUT の誤った出力の繰り返し数に依存するためである。 DUTを構成する CRAM ビットにおいてビットアップセットが発生したことは、DUT の構成の一部が書き換えられたことを意味する。画像処理において使用される回路のパスは、入力画像によって異なる。画像処理で、ビットアップセットによって書き換えられた回路部分が使用された場合に、SEFI が観測される。一定数以上の入力画像を扱うために、自動運転ロボットの挙動の監視は一定時間行う。

DUT 監視モジュールによって SEFI が観測された場合でも、それらの SEFI が自動運転システムに及ぼす影響は様々である。すべての SEFI が DUT の最終的な出力結果の誤りを引き起こすわけではないためである。モジュール間で画像の一部のデータが誤って転送されたとしても、DUT の最終的な計算において参照されないデータであれば、DUT は通常動作時と同様に正しい計算結果を出力する。SEFI が自動運転ロボットの動作を決定する DUT の出力結果に影響を与えない場合には、仮想環境上の自動運転ロボットは通常動作時と同様に車道外側線に沿った自動運転を続けることができる。一方で、自動運転ロボットの動作を決定する DUT が出力結果に影響を及ぼす場合には、それらの SEFI は仮想環境上の自動運転ロボットの異常な挙動として現れる。自動運転ロボットの誤った運転操作が繰り返されることで、自動運転ロボットの脱線が観測される。このため、一定時間をかけて仮想環境上で自動運転ロボットの挙動の監視を行う必要がある。

図 3.8 に、自動運転システムにおける CRAM のビットアップセットの発生から深刻な誤動作の観測までの流れを示す。赤色の十字の印はビットアップセット発生の位置を仮定している。エラー挿入実験および中性子照射実験では、ビットアップセットが発生した後で200 フレームの画像処理が行われる間、FPGA の回路の動作の監視と自動運転ロボットの挙動の監視を行う。DUT 監視モジュールが SEFI の監視を行うことと並行して、仮想環境上

図 3.8 深刻な誤動作の観測

で自動運転ロボットの挙動を監視する。自動運転ロボットの挙動の異常は、DUT の誤った 出力の繰り返しによって現れる。したがって、自動運転ロボットの異常な挙動として定義さ れる深刻な誤動作に対して、DUT の誤動作として定義される SEFI は、より早いタイミン グで観測される。SEFI が観測されたタイミングに関わらず、ビットアップセット発生後の 200 フレームの画像処理の間、深刻な誤動作の観測を行う。

図 3.8 に示す青色の矢印は、正常な走行の進路を示している。一方で赤色の矢印は、自動運転システムが正しい進路を決定できず、車道外側線から脱線していく時の進路の例を示している。200 フレームの画像処理が行われる間の自動運転ロボットの監視が終わった後で、自動運転ロボットの仮想環境上での座標を確認する。自動運転ロボットの座標に基づいて、自動運転ロボットが道路の決められた範囲から脱線しているかどうかを判断する。自動運転ロボットが決められた道路範囲から脱線している場合には、これらの SEFI を深刻な誤動作として分類する。

### 第4章 エラー挿入実験

エラー挿入実験では、意図的に任意の CRAM ビットを反転させることで、CRAM のビットアップセットと SEFI および深刻な誤動作の関係を明らかにすることを目指す。実験時間が限られている照射実験とは対照に、エラー挿入実験ではより多くのビットアップセットの影響を観測することが可能である。自動運転システムの構成ビットのうちビット反転が SEFI を引き起こす割合を示す Device Vulnerability Factor (DVF) を計算することで、ビットアップセットと SEFI の関係の評価する。

#### 4.1 実験方法

エラー挿入実験では SBU を評価対象とし、仮想運転環境における1回のテストランごとに1つのビット反転の影響を評価する。エラー挿入実験を通して、CRAM にエラーを挿入するタイミングはテストランが始まってから10番目の画像に固定した。テストランを開始後、DUTが10番目の画像を処理する途中で、SEM IPを使用してランダムに選択されたCRAM ビットを反転させる。その後の200フレーム分の画像処理の間、仮想運転環境で自動運転ロボットの挙動を監視する。1回のテストランが終了するとCRAMのデータを全て書き直して次のテストランを実施する。これをエラー挿入の必要サンプル数だけ繰り返して行う。

DUT の 3 つのモジュールのエッセンシャルビットに対してそれぞれエラー挿入を行い、各モジュールにおける DVF を計算する。なお、DUT1/DUT2/DUT3 は同じ回路構成であるため、以下では DUT1 を対象に計算した結果について説明する。CRAM のコンフィギューションビットのうち、DUT の構成に使用されるビットはエッセンシャルビットとして定義し、さらに、エッセンシャルビットのうちビット反転によって SEFI を引き起こすビットはクリティカルビットとして定義する。DVF は、エッセンシャルビットに対するクリティカルビットの割合を示しており、DUT の各モジュールにおける DVF の値  $DVF_i$  は、式 (4.1)で定義する [57]。i は各モジュールを意味しており、グレースケール化モジュール、Canny 法モジュール、車道外側線検出モジュールのいずれかである。 $N_{EB}$  はエッセンシャルビット、 $N_{CB}$  はクリティカルビットを表している。

$$DVF_i = \frac{N_{CB_i}}{N_{EB_i}},\tag{4.1}$$

同様に、深刻な誤動作に対しても  $DVF_i$  を計算するが、クリティカルビットはエッセンシャルビットのうちビット反転によって深刻な誤動作を引き起こすビットとして定義する。以上より、SEFI の DVF と深刻な誤動作の DVF を評価する。

表 4.1 エッセンシャルビットに対するエラー挿入実験で必要なサンプル数

| モジュール        | グレースケール化 | Canny 法 | 車道外側線検出 | 合計        |

|--------------|----------|---------|---------|-----------|

| $N_{EB}$     | 84,643   | 889,951 | 419,148 | 1,393,742 |

| $N_{inject}$ | 8,625    | 9,501   | 9,389   | 27,515    |

表 4.2 非エッセンシャルビットに対するエラー挿入実験で必要なサンプル数

| モジュール              | グレースケール化 | Canny 法 | 車道外側線検出 | 合計      |

|--------------------|----------|---------|---------|---------|

| $N_{nonEB}$        | 23,584   | 396,417 | 194,964 | 614,965 |

| $N_{inject-nonEB}$ | 6,825    | 9,377   | 9,153   | 25,355  |

ACME を用いた計算によるとエラーの挿入対象である Zynq-7000 の DUT は 2,012,199 bit で構成され、このうちの 1,396,106 bit がエッセンシャルビットである。数が非常に多く、全てのビットに対してエラー挿入を行うには膨大な時間がかかる。そこで、統計的に必要なサンプル数を計算し、ランダムにサンプリングした CRAM ビットを対象にエラー挿入を行った。必要なサンプル数は、式 (4.2) に基づいて信頼レベル 95%、誤差範囲 1% を満たすように決定した [58]。

$$N_{inject} = \frac{N_{EB}}{1 + e^2 \cdot \frac{N_{EB} - 1}{t^2 \cdot p \cdot (1 - p)}},$$

(4.2)

式 (4.2) で  $N_{EB}$  はエッセンシャルビット数、e は誤差範囲、t は信頼レベル、 $N_{inject}$  は  $N_{EB}$  に対する必要サンプル数を示している。式 (4.2) を用いて計算した各モジュールのエッセンシャルビットに対するエラー挿入の必要サンプル数を表 4.1 に示す。 $N_{EB}$  と  $N_{inject}$  は、各モジュールにおけるエッセンシャルビット数とエラー挿入の必要サンプル数を示している。

ビットアップセットが発生しても基本的に SEFI を引き起こすことはないとされる非エッセンシャルビットに対しても、式 (4.2) によって信頼レベル 95%、誤差範囲 1% を満たすサンプル数を計算し、同様のエラー挿入実験を実施した。DUT の各モジュールにおける非エッセンシャルビットの数と、エラー挿入実験に必要なサンプル数を表 4.2 に示す。

### 4.2 実験結果

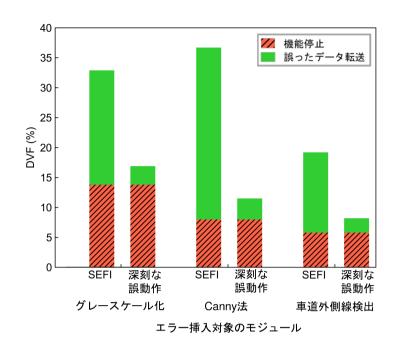

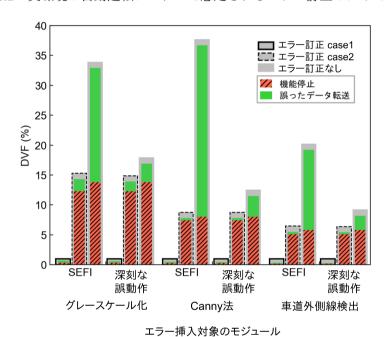

図 4.1 DUT における各モジュールの DVF

作につながっていることが分かる。一方で、SEFI として誤ったデータ転送が生じた場合、それが深刻な誤動作につながる可能性は比較的低かった。これは、いずれか 1 つのモジュールで機能停止が引き起こされた場合、DUT における全ての演算およびデータ転送が停止してしまうためであると考えられる。一方で、一部のデータ転送の誤りだけであれば、必ずしも DUT の最終的な出力に対して影響を与えるわけではないため、誤ったデータ転送が深刻な誤動作につながる可能性は低くなる。SEFI におけるモジュールの機能停止の割合は各モジュールでバラつきがあり、22% から 41% であった。

図 4.1 に示す各モジュールの DVF から、DUT 全体における SEFI と深刻な誤動作の DVF 値である  $DVF_{DUT}$  を式 (4.3) によって計算した。

$$DVF_{DUT} = \frac{\sum DVF_i \cdot N_{EB_i}}{\sum_i N_{EB_i}},$$

(4.3)

式 (4.3) において、i は DUT の各モジュールを表している。 $DVF_{DUT}$  は、DUT 全体のエッセンシャルビットにおけるクリティカルビットの割合である。式 (4.3) による計算の結果、SEFI と深刻な誤動作の  $DVF_{DUT}$  はそれぞれ 30.6% と 10.1% であった。このことから、10.1/30.6=33.0% の SEFI が最終的に深刻な誤動作を引き起こすことがわかる。6.1 節では、 $DVF_{DUT}$  を用いて、SEFI と深刻な誤動作のソフトエラー率を推測し、中性子照射実験でのソフトエラー率の測定値と比較する。

次に、表 4.2 の必要サンプル数に基づいて非エッセンシャルビットにエラー挿入を行ったところ、SEFI は観測されなかった。しかし、DUT の全てのビットに対してエラー挿入を実施した実験 [59] では、非常に低い確率で、非エッセンシャルビットのビット反転が SEFI を引き起こしたこと報告されている。このことから、エラー挿入のサンプル数を増やすと、今

表 4.3 ビット反転によって PS の動作停止を引き起こすビット

| SEM IP 用アドレス | フレームアドレス | ワードアドレス | ビットアドレス |

|--------------|----------|---------|---------|

| c001527b6a   | 5,415    | 91      | 10      |

| c001528b6b   | 5,416    | 91      | 11      |

| c00152950f   | 5,417    | 40      | 15      |

| c001529b69   | 5,417    | 91      | 9       |

| c00152ab27   | 5,418    | 91      | 7       |

| c00152ac5c   | 5,418    | 98      | 28      |

| c00152db27   | 5,421    | 89      | 7       |

| c001531b78   | 5,425    | 91      | 24      |

| c0015b0b0b   | 5,552    | 88      | 11      |

| c0015fdc17   | 5,629    | 96      | 23      |

回の評価対象の DUT でも同様の現象が観測できる可能性があるが、非エッセンシャルビットのビット反転が SEFI を引き起こすことは非常に稀であると考える。また、この結果に基づき、6.1 節におけるエラー挿入実験と中性子照射実験の比較でも、非エッセンシャルビットはビットアップセットによって SEFI を引き起こさないものとして扱う。

ところで、エッセンシャルビットに対するエラー挿入実験では例外的な故障として、エ ラー挿入後に PS の動作が停止する現象を確認した。この現象が発生した後では、実験対 象の FPGA ボードと PC の間でデータの転送を行うことができないため、エラー挿入実験 を継続できない。そのため、このような故障が発生した際は、一度 FPGA ボードの再起動 を行う必要がある。エラー挿入実験で約 28,000 回行ったエラー挿入に対して、ビット反転 によって PS の動作が停止するビットが 10 個存在した。これらの発生確率は非常に低いた め、4.2 節での DVF の計算の対象には含めずに例外的な故障として扱った。ビット反転に よって PS の動作の停止を引き起こすビットのアドレスを表 4.3 に示す。また、DUT1 の各 モジュールと DUT2、DUT3 のフレームアドレス範囲を表 4.4 に示す。表 4.3 と表 4.4 から ビット反転によって PS の動作停止を引き起こすビットは、グレースケール化モジュールと Canny 法モジュールの範囲に分布していることが分かる。CRAM のビットアップセットが PS に対して影響を与える原因として、PS と PL 間での画像データの転送のために用いた Xilinx 社の AXI Video Direct Memory Access (VDMA) IP の故障が考えられる [60]。このよ うに考える理由は、VDMA IP の誤動作によって DRAM に対して何らかの不正な操作が行 われる可能性があるためである。グレースケール化モジュールと Canny 法モジュールは車 道外側線検出モジュールよりも画像処理の上流に位置しており、最も上流の VDMA IP に対 して何らかの故障の影響が伝搬した可能性があると考える。CRAM ビットの反転が PS に 対して影響を与える現象は、DUTの全ての CRAM ビットに対してエラー挿入を実施した実 験 [59] でも確認されている。

別の例外的な故障として、DUT1にエラーを挿入したにも関わらず、DUT2や DUT3の

表 4.4 DUT1 の各モジュールおよび DUT2 と DUT3 の CRAM アドレス範囲

| モジュール    | フレームアドレス範囲    | 構成ビット数 |

|----------|---------------|--------|

| グレースケール化 | 5,392 - 5,445 | 1.1 M  |

| Canny 法  | 5,492 - 5,889 | 1.3 M  |

| 車道外側線検出  | 5,936 - 6,126 | 0.6 M  |

| DUT2     | 3,244 - 3,916 | 2.2 M  |

| DUT3     | 678 - 1,350   | 2.2 M  |

表 4.5 エラー挿入対象の DUT 以外の DUT で発生した SEFI

| エラー挿入    | 観測した | 観測数      |                  |  |

|----------|------|----------|------------------|--|

| モジュール    | 発生箇所 | 故障の種類    | <b>能光 (列 女</b> 人 |  |

|          | DUT2 | 誤ったデータ転送 | 1                |  |

| グレースケール化 | DU12 | 機能停止     | 0                |  |

|          | DUT3 | 誤ったデータ転送 | 11               |  |

|          | D013 | 機能停止     | 0                |  |

|          | DUT2 | 誤ったデータ転送 | 15               |  |

| Canny 法  |      | 機能停止     | 4                |  |

| Canny 12 | DUT3 | 誤ったデータ転送 | 0                |  |

|          |      | 機能停止     | 0                |  |

|          | DUT2 | 誤ったデータ転送 | 46               |  |

| 車道外側線検出  | DU12 | 機能停止     | 15               |  |

| 平旭江枫楸快山  | DUT3 | 誤ったデータ転送 | 0                |  |

|          | D013 | 機能停止     | 0                |  |

SEFI が引き起こされるケースを観測した。エラー挿入実験では DUT1 の CRAM ビットのアドレス範囲を計算し、ランダムに選択したビットに対してエラー挿入を実施した。そのため、エラー挿入により発生する SEFI は全て DUT1 で生じると考えていたが、エラー挿入を実施した約 28,000 ビットのうち 0.6% はビット反転によって DUT2 もしくは DUT3 に SEFI が発生した。このような DUT1 以外の DUT での SEFI の観測数の内訳を表 4.5 に示す。表 4.5 において、観測数は DUT1 以外の SEFI が観測された回数を示している。エラー挿入実験では、1 回のテストランで 1 つのビットを反転させている。したがって、表 4.5 における観測数は、DUT1 以外の SEFI を引き起こしたビットの数に等しい。Canny 法モジュールと車道外側線検出モジュールを対象としたエラー挿入では、DUT3 の SEFI は発生しなかった。また、車道外側線検出モジュールへのエラー挿入では、DUT2 の SEFI が比較的多く観測された。しかしながら、現時点でこれらの結果には規則性が見られない。これらのビットについては、ACME の計算では DUT1 の CRAM ビットであるにも関わらず、実際には DUT2、DUT3 の CRAM ビットである可能性が高いと考える。このようなビットが連

続的なアドレス分布になっておらず、ACME を用いたビットアドレスの計算で考慮できないことが原因であると考える。現時点では有効な対策は考えられなかった。

# 第5章 中性子照射実験

高精度な評価を行うことを目的として、東北大学 Cyclotron and Radioisotope Center(CYRIC) [61] にて中性子照射実験を行った。エラー挿入実験と中性子照射実験は同じ DUT と同じ評価環境を用いて実施した。中性子によって引き起こされる CRAM のビットアップセットのソフトエラー率および SEFI と深刻な誤動作のソフトエラー率の測定について述べる。

#### 5.1 実験方法

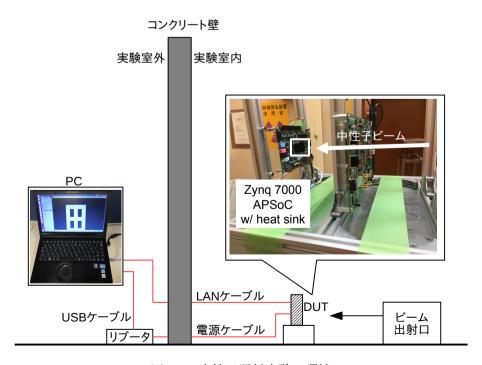

FPGA ボードに中性子ビームを照射する際の実験環境を図 5.1 に示す。中性子ビームを対象の FPGA ボードに照射する際、Gazebo が動作する PC は中性子ビームの影響を受けないように中性子を遮蔽するコンクリート壁によって隔たれた実験室外に設置し、FPGA ボードのみを中性子ビームのライン上に設置する。FPGA ボードと PC は LAN ケーブルで接続しており、PC 上の Gazebo と FPGA 上の自動運転システムの間でデータのやり取りが可能である。FPGA ボードは中性子の影響を受けて予期しない故障を引き起こすことがある。そのため、PC に接続したリブータによって FPGA ボードの電源を制御する。測定実験が続行できないような故障が発生した際は PC 側から FPGA ボードの再起動を行う。

中性子照射実験によってソフトエラー率を評価するために測定する値について説明する。

図 5.1 中性子照射実験の環境

Flux は単位時間あたりに単位面積を通過する中性子の数であり、単位は  $\mathbf{n} \cdot \mathbf{cm}^{-2} \cdot \mathbf{h}^{-1}$  である。例えば、地上でニューヨークにおける中性子の Flux は、 $20 \, \mathbf{n} \cdot \mathbf{cm}^{-2} \cdot \mathbf{h}^{-1}$  である [62]。 Fluence は、Flux を時間で積分した値であり、単位は  $\mathbf{n} \cdot \mathbf{cm}^{-2}$  である。ソフトエラーの発生確率は、衝突断面積 (CS:Cross Section) を用いて評価する。CS は 1 粒子により発生する単位時間あたりのソフトエラー数に等しい [63]。中性子照射実験での CS の測定値  $CS_{type}$  は、式 (5.1) によって定義する。

$$CS_{type} [cm^2 \cdot bit^{-1}] = \frac{N_{error}}{N_{bit} \times Fluence},$$

(5.1)

式 (5.1) において、type は、ソフトエラーの種類を表しており、ビットアップセット、SEFI、深刻な誤動作のいずれかである。 $N_{bit}$  はテスト対象のビット数を示しており、 $N_{error}$  はエラーの発生数を示している。

中性子照射実験では、ひとつの実験として SEFI と深刻な誤動作の CS 値である  $CS_{SEFI}$  と  $CS_{serious\ malfunction}$  の測定を行う。 CRAM でビットアップセットが検出された時、その後の 200 フレーム分の画像処理が行われる間で SEFI が発生するかどうか観測を行う。中性子照射実験ではビットアップセットが発生するタイミングが事前に予測できないため、CRAM でビットアップセットが長時間検出されない場合は 700 フレーム分の画像処理の終了後に一度 FPGA を再構成してテストランを再開する。

SEFI 観測のための 200 フレーム分の画像処理を行う間で、累積的に CRAM でビットアップセットが発生する可能性があるが、SEM IP はこのようなビットアップセットを検出することができない。これは反転したビットを訂正しないままにしておくと SEM IP の動作が停止することが原因である。また、同様の理由で SEM IP は、MCU/MBU も検出できない。そのため、SEFI と深刻な誤動作の CS の測定とは別に、個別の実験として SEM IP のエラー訂正機能を有効にして CRAM ビットアップセットの CS 値である  $CS_{bit\ upset}$  の測定も行った。SEFI と深刻な誤動作の CS の測定実験での 200 フレーム分の画像処理を行う間のビットアップセットの累積と検出不能な MCU/MBU の実験結果への影響は 5.2 節で述べる。

中性子照射実験では、測定対象ではない DRAM や BRAM でも同様にビットアップセットが発生する可能性がある。DRAM や BRAM のビットアップセットが原因で引き起こされる SEFI には、CRAM のビットアップセットによる SEFI とは違った特徴がある。まず、CRAM に格納されるデータは回路構成情報であるため基本的には回路の動作中に書き換わることはない。つまり、CRAM で発生したビットアップセットによって書き換えられた回路構成は、FPGA を再構成するまでそのままである。そのため、CRAM のビットアップセットによって書き換えられた回路によって引き起こされる SEFI は永遠に続く特徴がある。一方、DRAM と BRAM のデータは今回の実験体制では、画像 1 フレームごとに書き直されるため、これらのメモリのビットアップセットによって引き起こされた SEFI は一時的なものになると考えられる。この特徴に基づいて DRAM と BRAM のビットアップセット起因のSEFI を区別する。

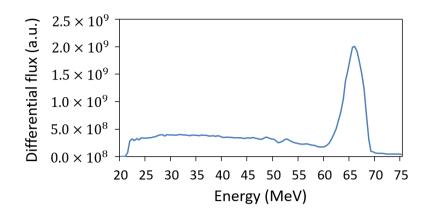

図 5.2 中性子ビームのスペクトラム

#### 5.2 実験結果

東北大学 CYRIC にて、70MeV の陽子ビームにより発生させた準単色の中性子ビームを Zynq-7000 に照射した。実験時の中性子ビームのスペクトラムを図 5.2 に示す。Flux のピークは 70MeV 付近であり、Zynq-7000 の設置位置における中性子ビームの Flux は、 $1.9 \times 10^8 \ n \cdot cm^{-2} \cdot h^{-1}$  であった。

表 5.1 に実験結果を示す。まず、SEM IP のエラー訂正機能を有効にしたビットアップセットの CS の測定を 4.1 時間行った。ビットアップセットの CS を測定する個別の実験では、評価対象のビットは Zynq-7000 の CRAM 全ビットの 26M ビットであり、Zynq-7000 の設置位置における Fluence は、 $8.0\times10^8~\mathrm{n\cdot cm^{-2}}$  であった。101 回の SBU、14 回の MCU、6 回の MBU がそれぞれ観測され、合計で 121 ビットのビットアップセットが観測された。式 (5.1) を用いて計算したビットアップセットの CS の測定値  $CS_{bit~upset}$  は  $5.9\times10^{-15}~\mathrm{cm^2\cdot bit^{-1}}$  で誤差範囲は  $\pm 9.1\%$  であった。この測定値は、Xilinx 社が行った同様の実験での測定値の誤差範囲内であった [16]。また、 $CS_{bit~upset}$  から、SEFI の観測のための 200 フレームの画像処理が行われる時間に累積するビットアップセットは平均 0.07 個であると推測される。そのため、このようなビットアップセットの累積の実験結果への影響は限定的であると判断した。

次に SEM IP のエラー訂正機能を無効にした状態で、自動運転システムにおける SEFI と深刻な誤動作の CS の測定を 13.4 時間行った。SEFI と深刻な誤動作の CS の測定は、3 つの DUT の 6.4M ビットを評価対象として行った。Zynq-7000 の設置位置における Fluence は、  $2.4\times10^8$  n·cm<sup>-2</sup> であった。SEFI は 21 回、深刻な誤動作は 7 回観測された。式 (5.1) を用いて計算した SEFI と深刻な誤動作の CS の測定値  $CS_{SEFI}$  と  $CS_{serious\ malfunction}$  は、それぞれ  $1.4\times10^{-15}$  cm<sup>2</sup>·bit<sup>-1</sup> と  $4.5\times10^{-16}$  cm<sup>2</sup>·bit<sup>-1</sup> であった。 $CS_{bit\ upset}$  との比較から、ビットアップセットの約 23% が SEFI を引き起こすことがわかった。さらに、SEFI の約 33% は

表 5.1 中性子照射実験の結果

| Error typo                            | ビットアップセット (個別の実験)     |                       |                       |                       | SEFI                  | 深刻な誤動作                |

|---------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| Error type                            | total                 | SBU                   | MCU                   | MBU                   | SEIT                  | 休刻な映動性                |

| 実験時間 (h)                              | 4.1                   | 4.1                   | 4.1                   | 4.1                   | 13.4                  | 13.4                  |

| Fluence (n $\cdot$ cm <sup>-2</sup> ) | $8.0 \times 10^{8}$   | $8.0 \times 10^{8}$   | $8.0 \times 10^{8}$   | $8.0 \times 10^{8}$   | $2.4 \times 10^{9}$   | $2.4 \times 10^9$     |

| 対象のビット数                               | 26 M                  | 26 M                  | 26 M                  | 26 M                  | 6.4 M                 | 6.4 M                 |

| 観測イベント数                               | 121                   | 101                   | 14                    | 6                     | 21                    | 7                     |

| $CS (cm^2 \cdot bit^{-1})$            | $5.9 \times 10^{-15}$ | $4.9 \times 10^{-15}$ | $6.8 \times 10^{-16}$ | $2.9 \times 10^{-16}$ | $1.4 \times 10^{-15}$ | $4.5 \times 10^{-16}$ |

| 誤差範囲 (%)                              | ± 9.1                 | ± 10                  | ± 27                  | ± 41                  | ± 22                  | ± 38                  |

最終的に深刻な誤動作を引き起こすことがわかった。

CRAMのビットアップセットと SEFI の関係性を検証するために、ビットアップセットの検出時間と発生箇所の記録と、SEFI の発生時間と発生箇所の記録を比較した。その結果、観測された SEFI の半分以上では、ビットアップセットの検出時間と発生箇所が、SEFI の発生時間と発生箇所にそれぞれ一致していた。したがって、観測された SEFI は CRAM のビットアップセットによって引き起こされた可能性が高いと考える。ビットアップセットの検出時間と発生箇所が SEFI の発生時間と発生箇所にそれぞれ一致していないものについては、SEFI の発生が入力画像に依存することや、SEM IP で検出不能な MCU の影響などが原因として考えられる。例えば、ビットアップセットが観測された後で遅れて SEFI が観測されるケースが存在した。これは、入力画像によって、使用される回路のパスが変わることが原因で、CRAM のビットアップセットによって書き換えられた回路パスがしばらく経ってから画像処理中に使われた時点で SEFI が観測されたと考える。また、観測されたビットアップセットの発生箇所が DUT の外であるにも関わらず、DUT の SEFI が観測されたケースも存在した。これは、ACME による DUT のアドレス計算の誤差、200 フレーム間の SEFI 監視中の累積的なビットアップセット、SEM IP が検出できない MCU が影響していると考える。

### 第6章 ソフトエラー率の分析

エラー挿入実験と中性子照射実験の結果を CS に基づいて比較する。エラー挿入実験と中性子照射実験の結果の比較から提案する評価手法の妥当性を検証する。エラー挿入実験に基づいて、エラー訂正回路の有効性について述べる。エラー訂正を行った場合の DVF とエラー訂正を行わなかった場合の DVF と比較することでエラー訂正回路の有効性を検証する。

#### 6.1 エラー挿入実験と中性子照射実験の結果の比較

まず、エラー挿入実験によって、中性子照射実験で観測された SEFI の再現性を確かめた。中性子照射実験において SEFI を引き起こしたビットアップセットの検出時間と発生箇所の記録をもとにエラー挿入を行った。ビットアップセットの記録とは、ビットアップセットが発生した時に処理が行われていた画像のフレーム番号と、ビットアップセットが発生した CRAM ビットのアドレスである。SEM IP を用いて、同じアドレスの CRAM ビットに対して、同じフレーム番号の画像を処理するタイミングでエラー挿入を行うことで、中性子照射実験で観測されたすべての SEFI を再現できることを確認できた。

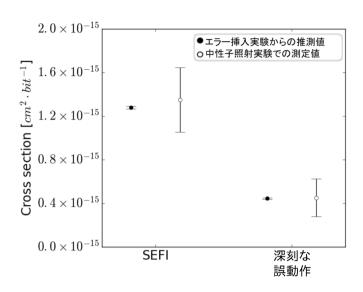

次に、エラー挿入実験で得た DVF をもとに SEFI と深刻な誤動作の CS を推定し、中性子照射実験での CS の測定値と比較することで提案評価手法の妥当性を確かめた。エラー挿入実験で得た DUT の DVF と中性子照射実験で得たビットアップセットの CS から SEFI と深刻な誤動作の CS を推定し、中性子照射実験での測定値と比較する。エラー挿入実験で得た DUT1 全体における SEFI と深刻な誤動作の DVF は、それぞれ 30.6% と 10.1% であった。中性子照射実験で得たビットアップセットの CS の測定値  $CS_{bit\ upset}$  は  $5.9\times10^{-15}\ {\rm cm}^2\cdot{\rm bit}^1$  であった。これらの値から式 (6.1) を用いて CS の推定値  $\sigma_{type}$  を求めた。なお、式 (6.1) で type は、SEFI もしくは深刻な誤動作である。なお、式 (6.1) では、4.2 節のエラー挿入実験で確認したとおりに、非エッセンシャルビットでビットアップセットが発生しても SEFI が引き起こされないことを前提としている。

$$\sigma_{type} = CS_{bit\ upset} \times DVF_{type} \times \frac{N_{EB}}{N_{EB} + N_{nonEB}}$$

$$= CS_{bit\ upset} \times \frac{N_{CB_{type}}}{N_{EB} + N_{nonEB}}$$

(6.1)

式 (6.1) を用いた計算によると、エラー挿入実験から推測される SEFI と深刻な誤動作の CS の推定値  $\sigma_{SEFI}$ 、 $\sigma_{serious\ malfunction}$  はそれぞれ  $1.3\times10^{-15}\ {\rm cm^2\cdot bit^{-1}}$  と  $4.4\times10^{-16}\ {\rm cm^2\cdot bit^{-1}}$  であった。エラー挿入実験では、ランダムにサンプリングした CRAM ビットを反転させて いるため、 $\sigma_{SEFI}$  と  $\sigma_{serious\ malfunction}$  には  $\pm$  1% の誤差がある。中性子照射実験では、SEFI の CS の測定値  $CS_{SEFI}$  は  $1.4\times10^{-15}\ {\rm cm^2\cdot bit^{-1}}$  で誤差範囲  $\pm$  22%、深刻な誤動作の CS の

図 6.1 SEFI と深刻な誤動作の CS の測定値と推定値の比較

測定値 CS serious malfunction は  $4.4 \times 10^{-16}$  cm<sup>2</sup>·bit<sup>-1</sup> で誤差範囲  $\pm$  38% であった。エラー挿入 実験との比較を図 6.1 に示す。エラー挿入実験から推定した SEFI と深刻な誤動作の CS は、中性子照射実験で得られた結果の誤差範囲内であることがわかる。

また、3.4.2 節で述べたように矩形内に DUT を配置するフロアプランでは、DUT 内で MBU/MCU が発生する可能性が高くなると考えられる。SEM IP を用いて MBU/MCU を検 出することができないため、中性子照射実験の結果には SBU だけでなく MBU/MCU の影響も含んでいる。しかし、図 6.1 に示すように、SBU のみを対象としたエラー挿入実験と中性子照射実験の結果が誤差範囲内で一致したことから、矩形内に DUT を配置するフロアプランによる DUT 内での MBU/MCU の増加の影響は限定的なものであると考える。

以上より、提案する評価手法によって自動運転システムにおける CRAM ビットアップ セットの影響を正確に評価できることを実証した。

### 6.2 エラー訂正回路

本研究で使用した SEM IP のように、SRAM 型 FPGA の各ベンダはソフトエラー訂正 ツールを提供している [64]。これらのエラー訂正ツールは、DUT と同じ FPGA 内に実装されるオンチップのエラー訂正回路である。本節では、このようなオンチップのエラー訂正回路の有効性を評価する。

エラー訂正回路の有効性を評価するために、4章のエラー挿入実験で対象としたエッセンシャルビットと同様のエッセンシャルビットに対してエラー挿入を行う。エラー訂正回路を評価する際の実験方法は、基本的には4章で述べたエラー訂正なしのエラー挿入実験と同様とするが、エラー挿入後に後述のエラー訂正の過程を追加した。エラー訂正の評価実験で

は、SEM IP のエラー訂正機能を有効にはせず、エラー挿入によって反転させたビットを一定の時間経過後で再び反転させて元の状態に戻す手法をとった。このようなエラー訂正を行った理由は、SEM IP のエラー訂正を有効にするためには再び論理合成を行う必要があり、この過程でエッセンシャルビットのアドレスが変わってしまうためである。

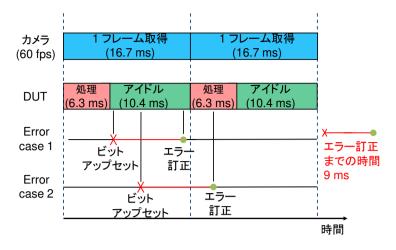

SEM IP のエラー訂正機能を使わずにビット反転を訂正する今回の手法では、エラー挿入後に反転させたビットを再び反転させるまでの時間を決める必要がある。これは、SEM IP のエラー訂正機能を有効にした際にエラー検出とエラー訂正に要する時間を考慮して決定した。実験対象とした Zynq-7000 の PL で SEM IP は 100MHz で動作する。この場合に SEM IP がエラー検出に要する最大の時間は 8.0ms で、エラー訂正に要する時間は 0.6ms である [55]。したがって、SEM IP は 9ms 以内にエラー訂正を完了することができる。そこで、エラー訂正の評価実験では、SEM IP の最大遅延時間を想定して、エラーを挿入したビットを再び元に戻すまでの時間間隔を 9ms に設定した。

実際の環境での自動運転システムにおけるビットアップセットの発生とエラー訂正の実 施状況を考慮して実験条件について考える。図 6.2 に、60fps のカメラを搭載した自動運転 システムで想定されるエラー訂正のタイミングを示す。DUT が 1 フレームの画像処理に要 する時間は 6.3ms であり、60fps のカメラが画像取得する間隔の 16.7ms よりも短い。その ため、DUT は1フレーム分の画像処理が終わった後、カメラが次の画像を取得するまでは 間は、アイドル状態になることを想定した。ビットアップセットが発生した際のエラー訂 正のタイミングは、図 6.2 の 'Error case 1' と 'Error case 2' を想定した。'Error case 1' で は、ビットアップセットが発生するタイミングとエラー訂正が行われるタイミングは両方 とも DUT がアイドル状態の時間内であることを想定している。DUT のアイドル状態の時 間 (10.4ms) とエラー訂正にかかる時間 (9ms) を考慮して、ビットアップセットが発生する タイミングは、DUT がアイドル状態に入った後の 10.4-9=1.4ms 以内である。DUT が次 の画像処理を行う前にエラーが訂正されるため、ビットアップセットは DUT の画像処理中 には影響を及ぼさない。'Error case 2' では、ビットアップセットが発生するタイミングは 'Error case 1' 以外であり、エラーが訂正されていない状態で、DUT が画像処理を行う状況 を想定している。'Error case 1' の条件でエラー訂正の実験を行う際は、エラー挿入を行う前 に DUT の処理を停止させて対象のエッセンシャルビットにエラー挿入を行い、DUT の処 理を止めたまま 9ms 秒後に再びそのエッセンシャルビットを反転させ元の状態に戻す。そ の後、DUT の処理を再開させることで DUT の画像処理の時間中にビットアップセットの 影響を受けない状況を実現した。'Error case 1' では DUT が処理を行わない間にエラーが訂 正されるため、DUT内で行われる画像データの転送はほとんど影響を受けないと予想され るが、DUT 外部との配線に関わるビットも存在するため、このようなビットでビットアッ プセットが発生した場合には DUT の故障が引き起こされる可能性があると考えられる。一 方、'Error case 2' の条件でエラー訂正の実験を行う際は、DUT が画像処理を行っている間 のランダムなタイミングでエッセンシャルビットに対してエラーの挿入を行い、9ms 秒後

図 6.2 実環境の自動運転システムで想定されるエラー訂正のタイミング

図 6.3 エラー訂正を行った場合の各モジュールの DVF

に対象のエッセンシャルビットを元の状態に戻す。実際の自動運転システムでも同様に、 'Error case 1' もしくは 'Error case 2' の状況で SBU が発生することが考えられる。ビットアップセットの影響は画像処理の時間に影響がない場合と、1 フレームの画像処理に影響が及ぶ場合に分けられる。そのため、この 2 つの条件でエラー挿入実験を実施し、それぞれの場合で式 (4.1) を用いて各モジュールの DVF 値である  $DVF_i$  の算出を行い、エラー訂正回路の有効性を評価した。

図 6.3 に 'Error case 1' と 'Error case 2' の条件でエラー訂正を行った際の各モジュールの DVF を示す。比較のためにエラー訂正なしのエラー挿入実験の結果も合わせて示している。図 6.3 から、エラー訂正のタイミングが 'Error case 1' と 'Error case 2' のいずれかに関わらず、エラー訂正回路によって大幅に DVF を減少させることができることが分かる。しかし、深刻な誤動作では、'Error case 1' と 'Error case 2' において、エラー訂正回路の有効

性に差があることが分かる。ビットアップセットの影響が DUT の画像処理中にもおよぶ 'Error case 2' の場合では、エラー訂正によって深刻な誤動作を大幅に防ぐことはできていない。一方で、DUT で画像処理が行われない時間にエラーの訂正が行われる 'Error case 1' では、深刻な誤動作の DVF を大幅に減少させることができた。図 6.3 から、これらの違いは、モジュールの機能停止に対するエラー訂正回路の有効性であることが分かる。ビットアップセットが起きた後で画像処理が行われると、モジュールの機能停止がすぐに引き起こされると考えられる。そのため、ビットアップセットの影響が画像処理時間に及ぶ 'Error case 2'では、エラー訂正によってモジュールの機能停止を防ぐことが難しい。しかし、'Error case 1'のエラー訂正のように、画像処理モジュールが動作をしていない間にエラー訂正を行うことで、モジュールの機能停止の発生を大幅に防ぐことができる。

以上のことから、自動運転システムの信頼性を向上さるためにエラー訂正回路を用いる場合には、エラー訂正のタイミングが重要であり、DUTがアイドル状態の間にエラー訂正を完了することができる高速な訂正が求められることがわかった。さらに、4.2 節で述べた、ビット反転によって PS の動作の停止が引き起こされたビットについて、ビットアップセットの影響が DUT の画像処理時間に及ばない 'Error case 1'では、システムの故障が観測されなかった。この結果は、VDMA IP の故障によって DRAM に対して不正操作が行われることが原因で PS に故障を引き起こすという考察に一貫している。 'Error case 1'では VDMA IP が停止している間にエラーの訂正が行われるため PS の故障も発生しなかったことが考えられる。

### 第7章 まとめ

本研究では、SRAM 型 FPGA に実装した画像処理に基づく自動運転システムを対象に、CRAM のビットアップセットの影響を評価した。提案する評価手法によって、FPGA の論理機能の故障である SEFI のうち、自動運転ロボットの決められた道路範囲からの脱線を引き起こす SEFI を深刻な誤動作として分類し評価することを目指した。

提案するソフトエラー評価環境は、1 台の PC と 1 台の FPGA ボードによって構成される。画像処理に基づいて車道外側線検出を行い、道路車線に沿ってレーンキープ制御を行う自動運転システムを FPGA に実装した。PC では、3D シミュレータ Gazebo を用いて仮想環境上に自動運転ロボットと運転環境を構築した。FPGA ボードと PC 間の相互の通信によって仮想環境上でロボットの自動運転を実現した。

提案する評価環境を用いて、人工的にソフトエラーの発生を再現するエラー挿入実験と中性子照射実験を実施した。エラー挿入実験では、DUTを構成する CRAM ビットのうち、31% がビット反転によって自動運転システムの SEFI を引き起こすことがわかった。さらに、これらの SEFI のうち 33% が自動運転ロボットの脱線を意味する深刻な誤動作を引き起こした。中性子照射実験では SEFI と深刻な誤動作のソフトエラー率 CS を測定した。中性子照射実験で測定した SEFI と深刻な誤動作の CS と、エラー挿入実験から推測される CS の比較を行ったところ、エラー挿入実験からの推測値が中性子照射実験での測定値の誤差範囲内に収まっていることを確認した。このことから、提案する仮想環境を用いたソフトエラー評価手法の有用性を実証した。

また、CRAMのエラー訂正回路の有効性を検証した。エラー訂正回路によって SEFI の発生を大幅に防ぐことができることが分かった。さらに、深刻な誤動作の発生を防ぐためには、エラー訂正を実行するタイミングが重要であることが分かった。さらに、DUT が画像処理を行わないアイドル状態の時にエラー訂正を実施することで、深刻な誤動作の発生を大幅に防ぐことができることを明らかにした。

今後の課題としては、現実的な自動運転システムを構築して、ソフトエラーの影響を評価することである。信号機や歩行者なども考慮した道路環境において、複雑な画像処理や細かいモータ制御なども統合した自動運転システムの信頼性を評価することで、現実的な自動運転におけるソフトエラーの影響を見積もることに繋がると考える。

# 謝辞

本研究を進めるにあたり、ご指導いただきました高知工科大学システム工学群 密山幸男教授、廖望氏(現・東京大学大学院工学系研究科 附属光量子科学研究センター 特任研究員)に心より深く感謝いたします。また、ご助言いただくとともに日頃からおせわになりました。高知工科大学システム工学群 橘昌良教授に深く感謝いたします。また、橘・密山研究室の皆様には、日頃から様々な意見を頂きました。心より感謝いたします。

# 参考文献

- [1] R. Baumann, "The Impact of Technology Scaling on Soft Error Rate Performance and Limits to the Efficacy of Error Correction," in *Digest. International Electron Devices Meeting*, pp. 329–332, Dec. 2002.

- [2] H. Ando, R. Kan *et al.*, "Validation of hardware error recovery mechanisms for the sparc64 v microprocessor," in 2008 IEEE International Conference on Dependable Systems and Networks With FTCS and DCC (DSN), pp. 62–69, June 2008.

- [3] 上村大樹, 菅竜二, "大規模計算機向け半導体デバイスにおけるソフトエラー-最高レベルの信頼性を求めて-," ソフトエラー (などの LSI における放射線効果) に関する第 2 回勉強会, 2012.

- [4] M. Hashimoto and W. Liao, "Soft Error and Its Countermeasures in Terrestrial Environment," in 2020 25th Asia and South Pacific Design Automation Conference (ASP-DAC), pp. 617–622, Mar. 2020.

- [5] D. Krueger, E. Francom *et al.*, "Circuit Design for Voltage Scaling and SER Immunity on a Quad-Core Itanium Processor," in *2008 IEEE International Solid-State Circuits Conference Digest of Technical Papers*, pp. 94–95, Jan. 2008.

- [6] J. Wilkinson and S. Hareland, "A Cautionary Tale of Soft Errors Induced by SRAM Packaging Materials," *IEEE Transactions on Device and Materials Reliability*, vol. 5, no. 3, pp. 428–433, 2005.

- [7] V. Bandeira, I. Oliveira *et al.*, "Soft Error Reliability Analysis of Autonomous Vehicles Software Stack," *IEEE/IFIP International Conference on VLSI and System-on-Chip, VLSI-SoC*, vol. 2019-October, pp. 253–254, Oct. 2019.

- [8] ISO, ISO 26262:2011 Road vehicles Functional safety Part 1 to Part 10. ISO, Geneva, Switzerland, 2011, no. ISO 26262.

- [9] 公益社団法人 自動車技術会, "自動車用運転自動化システムのレベル分類及び定義," *JASO* テクニカルペーパ, 2018.

- [10] 村松彰二, 志磨健, "自動運転に向けた画像センシング," 計測と制御, vol. 54, no. 11, pp. 849-853, 2015.

- [11] Y. Lyu, L. Bai *et al.*, "Real-Time Road Segmentation Using LiDAR Data Processing on an FPGA," in 2018 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1–5, May 2018.

- [12] C. Khongprasongsiri, P. Kumhom *et al.*, "A Hardware Implementation for Real-time Lane Detection Using High-level Synthesis," in 2018 International Workshop on Advanced Im-

- age Technology (IWAIT), May 2018.

- [13] J. Fowers, G. Brown *et al.*, "A Performance and Energy Comparison of FPGAs, GPUs, and Multicores for Sliding-Window Applications," in *Proceedings of the ACM/SIGDA International Symposium on Field Programmable Gate Arrays*, 2012, pp. 47–56, Feb. 2012.

- [14] C. Slayman, "Soft Error Trends and Mitigation Techniques in Memory Devices," in *2011 Proceedings Annual Reliability and Maintainability Symposium*, pp. 1–5, Apr. 2011.

- [15] S. Srinivasan, A. Gayasen *et al.*, "Improving Soft-Error Tolerance of FPGA Configuration Bits," in *IEEE/ACM International Conference on Computer Aided Design, 2004. ICCAD-2004.*, pp. 107–110, Nov. 2004.

- [16] Xilinx, "Device Reliability Report," UG116, Second Half 2019, April 2020.

- [17] V. Vlagkoulis, A. Sari *et al.*, "Single Event Effects Characterization of the Programmable Logic of Xilinx Zynq-7000 FPGA Using Very/Ultra High-Energy Heavy Ions," *IEEE Transactions on Nuclear Science*, vol. 68, no. 1, pp. 36–45, 2021.

- [18] H. Quinn, T. Fairbanks *et al.*, "Single-Event Effects in Low-Cost, Low-Power Microprocessors," in *2014 IEEE Radiation Effects Data Workshop (REDW)*, pp. 20–28, July 2014.

- [19] D. S. Lee, M. King *et al.*, "Single-Event Characterization of 16 nm FinFET Xilinx Ultra-Scale+ Devices with Heavy Ion and Neutron Irradiation," in *2018 IEEE NSREC Radiation Effects Data Workshop*, pp. 275–282, Dec. 2018.

- [20] C. Cai, S. Gao *et al.*, "SEE Sensitivity Evaluation for Commercial 16 nm SRAM-FPGA," *Electronics*, vol. 8, no. 12, p. 1531, Dec. 2019. [Online]. Available: https://www.mdpi.com/2079-9292/8/12/1531

- [21] L. A. Tambara, P. Rech *et al.*, "Analyzing the Impact of Radiation-Induced Failures in Programmable SoCs," *IEEE Transactions on Nuclear Science*, vol. 63, no. 4, pp. 2217–2224, 2016.

- [22] A. E. Wilson and M. Wirthlin, "Neutron Radiation Testing of Fault Tolerant RISC-v Soft Processor on Xilinx SRAM-based FPGAs," *Proceedings 2019 IEEE Space Computing Conference*, SCC 2019, pp. 25–32, July 2019.

- [23] Á. B. de Oliveira, L. A. Tambara *et al.*, "Evaluating Soft Core RISC-V Processor in SRAM-Based FPGA Under Radiation Effects," *IEEE Transactions on Nuclear Science*, vol. 67, no. 7, pp. 1503–1510, July 2020.

- [24] L. A. Aranda, A. Sánchez-Macián *et al.*, "ACME: A Tool to Improve Configuration Memory Fault Injection in SRAM-Based FPGAs," *IEEE Access*, vol. 7, pp. 128153–128161, Sept. 2019.

- [25] H. Cho, "Impact of Microarchitectural Differences of RISC-V Processor Cores on Soft Error Effects," *IEEE Access*, vol. 6, pp. 41 302–41 313, July 2018.

- [26] B. Du, S. Azimi et al., "On the Reliability of Convolutional Neural Network Implementa-

- tion on SRAM-based FPGA," in 2019 IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), pp. 143–148, Oct. 2019.

- [27] I. C. Lopes, F. Benevenuti *et al.*, "Reliability Analysis on Case-study Traffic Sign Convolutional Neural Network on APSoC," in *2018 IEEE 19th Latin-American Test Symposium* (*LATS*), pp. 7–12, Mar. 2018.

- [28] F. Libano, B. Wilson *et al.*, "Selective Hardening for Neural Networks in FPGAs," *IEEE Transactions on Nuclear Science*, vol. 66, no. 1, pp. 216–222, 2019.

- [29] H.-B. Wang, Y.-S. Wang *et al.*, "Impact of Single-Event Upsets on Convolutional Neural Networks in Xilinx Zynq FPGAs," *IEEE Transactions on Nuclear Science*, vol. 68, no. 4, pp. 394–401, 2021.

- [30] F. Libano, P. Rech *et al.*, "How Reduced Data Precision and Degree of Parallelism Impact the Reliability of Convolutional Neural Networks on FPGAs," *IEEE Transactions on Nuclear Science*, vol. 68, no. 5, pp. 865–872, 2021.

- [31] C. Bolchini, L. Cassano *et al.*, "Error Modeling for Image Processing Filters accelerated onto SRAM-based FPGAs," in 2020 IEEE 26th International Symposium on On-Line Testing and Robust System Design (IOLTS), pp. 140–145, July 2020.

- [32] L. A. Aranda, P. Reviriego *et al.*, "Error Detection Technique for a Median Filter," *IEEE Transactions on Nuclear Science*, vol. 64, no. 8, pp. 2219–2226, 2017.

- [33] C. Aguero, N. Koenig *et al.*, "Inside the Virtual Robotics Challenge: Simulating Real-Time Robotic Disaster Response," *Automation Science and Engineering, IEEE Transactions on*, vol. 12, no. 2, pp. 494–506, April 2015.

- [34] T. Tanaka, W. Liao *et al.*, "Impact of Neutron-Induced SEU in FPGA CRAM on Image-Based Lane Tracking for Autonomous Driving: From Bit Upset to SEFI and Erroneous Behavior," *IEEE Transactions on Nuclear Science*, vol. 69, no. 1, pp. 35–42, 2022.

- [35] 尾崎太樹, 飯田全広, 泉知論, 長名保範, 佐野健太郎, 柴田裕一郎, 末吉敏則, 中原啓貴, 張山昌論, 丸山勉, 密山幸男, 本村真人, 山口佳樹, 渡邉実, FPGA の原理と構成. 株式会社オーム社, 2017.

- [36] "XILINX. Zynq-7000 All Programmable SoC, 2017," http://www.xilinx.com/products/silicon-devices/soc/zynq-7000.html.

- [37] Xilinx, "7 Series FPGAs Configurable Logic Block," UG474 (v1.8), Sept. 2016.

- [38] F. Siegle, T. Vladimirova *et al.*, "Mitigation of Radiation Effects in SRAM-Based FPGAs for Space Applications," *ACM Comput. Surv.*, vol. 47, no. 2, jan 2015. [Online]. Available: https://doi.org/10.1145/2671181

- [39] M. Wirthlin, E. Johnson *et al.*, "The Reliability of FPGA Circuit Designs in the Presence of Radiation Induced Configuration Upsets," *IEEE Symposium on FPGAs for Custom Computing Machines, Proceedings*, vol. 2003-January, pp. 133–142, Jan. 2003.

- [40] L. A. Aranda, N.-J. Wessman *et al.*, "Analysis of the Critical Bits of a RISC-V Processor Implemented in an SRAM-Based FPGA for Space Applications," *Electronics*, vol. 9, no. 1, p. 175, 2020. [Online]. Available: https://www.mdpi.com/2079-9292/9/1/175

- [41] H. Quinn and M. Wirthlin, "Validation Techniques for Fault Emulation of SRAM-based FPGAs," *IEEE Transactions on Nuclear Science*, vol. 62, no. 4, pp. 1487–1500, 2015.

- [42] F. Benevenuti and F. L. Kastensmidt, "Comparing Exhaustive and Random Fault Injection Methods for Configuration Memory on SRAM-based FPGAs," in *2019 IEEE Latin American Test Symposium (LATS)*, pp. 1–6, May 2019.

- [43] P. S. Ostler, M. P. Caffrey *et al.*, "SRAM FPGA Reliability Analysis for Harsh Radiation Environments," *IEEE Transactions on Nuclear Science*, vol. 56, no. 6, pp. 3519–3526, 2009.

- [44] J. Mogollon, H. Guzmn-Miranda et al., in 2011 12th European Conference on Radiation and Its Effects on Components and Systems.

- [45] M. Alderighi, S. D'Angelo *et al.*, "A fault injection tool for SRAM-based FPGAs," in *9th IEEE On-Line Testing Symposium*, 2003. IOLTS 2003., pp. 129–133, July 2003.

- [46] A. Lindoso, L. Entrena *et al.*, "A Hybrid Fault-Tolerant LEON3 Soft Core Processor Implemented in Low-End SRAM FPGA," *IEEE Transactions on Nuclear Science*, vol. 64, no. 1, pp. 374–381, 2017.

- [47] M. Alderighi, S. D'Angelo *et al.*, "The FLIPPER Fault Injection Platform: Experiences and Knowledge from a Ten-year Project," in *ARCS 2017; 30th International Conference on Architecture of Computing Systems*, Apr. 2017.

- [48] A. Prez-Celis, C. Thurlow *et al.*, "Emulating Radiation-Induced Multicell Upset Patterns in SRAM FPGAs With Fault Injection," *IEEE Transactions on Nuclear Science*, vol. 68, no. 8, pp. 1594–1599, 2021.

- [49] A. E. Wilson, S. Larsen *et al.*, "Neutron Radiation Testing of a TMR VexRiscv Soft Processor on SRAM-Based FPGAs," *IEEE Transactions on Nuclear Science*, vol. 68, no. 5, pp. 1054–1060, 2021.

- [50] J. D. Anderson, J. C. Leavitt *et al.*, "Neutron Radiation Beam Results for the Xilinx UltraScale+ MPSoC," in *2018 IEEE Radiation Effects Data Workshop (REDW)*, 2018, pp. 194–200, July 2018.

- [51] E. Johnson, M. Caffrey *et al.*, "Accelerator Validation of an FPGA SEU Simulator," *IEEE Transactions on Nuclear Science*, vol. 50, no. 6 I, pp. 2147–2157, 2003.

- [52] F. Lima, C. Carmichael *et al.*, "A fault injection analysis of virtex fpga tmr design methodology," in *RADECS 2001. 2001 6th European Conference on Radiation and Its Effects on Components and Systems (Cat. No.01TH8605)*, pp. 275–282, Sept. 2001.

- [53] T. Tanaka, I. Ikeno et al., "Development of Autonomous Driving System Using Pro-

- grammable SoCs," in 2019 International Conference on Field-Programmable Technology (ICFPT), pp. 453–456, Dec. 2019.

- [54] A. Yamawaki and S. Serikawa, "A Describing Method of An Image Processing Software in C for A High-level Synthesis Considering A Function Chaining," *IEICE Transactions on Information and Systems*, vol. E101D, no. 2, pp. 324–334, Feb. 2018.

- [55] Xilinx, "Soft Error Mitigation Controller v4.1 LogiCORE IP Product Guide," *PG036*, April 2018.

- [56] T. Bates and C. P. Bridges, "Single event mitigation for Xilinx 7-series FPGAs," in 2018 *IEEE Aerospace Conference*, pp. 1–12, Mar. 2018.

- [57] Y. P. Chen, P. Maillard *et al.*, "64 MeV Proton Single-Event Upset Characterization of Customer Memory Interface Design on Xilinx XCKU040 FPGA," in 2017 IEEE Radiation Effects Data Workshop (REDW), pp. 144–147, July 2017.

- [58] R. Leveugle, A. Calvez *et al.*, "Statistical Fault Injection: Quantified Error and Confidence," in *2009 Design, Automation Test in Europe Conference Exhibition*, pp. 502–506, April 2009.

- [59] S. T. Fleming and D. Thomas, "Injecting FPGA Configuration Faults in Parallel," in 2018 International Conference on Field-Programmable Technology (FPT), pp. 198–205, Dec. 2018.

- [60] S. Ramagond, S. Yellampalli *et al.*, "A Review and Analysis of Communication Logic between PL and PS in ZYNQ AP SoC," in *2017 International Conference On Smart Technologies For Smart Nation (SmartTechCon)*, pp. 946–951, Aug. 2017.

- [61] Y. Sakemi, M. Itoh *et al.*, "High Intensity Fast Neutron Beam Facility at CYRIC," *Nuclear Technology*, vol. 173, no. 2, pp. 210–217, July 2014.

- [62] M. Cecchetto, R. G. Alía *et al.*, "Impact of Energy Dependence on Ground Level and Avionic SEE Rate Prediction When Applying Standard Test Procedures," *Aerospace*, vol. 6, no. 11, 2019.

- [63] 小林和淑, "半導体の耐性試験:加速器によるシングルイベント耐性の実測評価 (特集 広がる加速器の利用 中性子) (加速器中性子源の利用)," *journal of the Particle Accelerator Society of Japan*, vol. 13, no. 4, pp. 245–252, 2016. [Online]. Available: https://ci.nii.ac.jp/naid/40021081083/

- [64] A. M. Keller and M. J. Wirthlin, "Single-Event Characterization of a Stratix 10 FPGA Using Neutron Irradiation," in 2019 IEEE Radiation Effects Data Workshop, pp. 173–178, July 2019.