細粒度パワーゲーティング機構を備えた自己同期型パイプラインと その実装評価

宮城 桂<sup>†a)</sup> 岩田 誠<sup>††</sup> 三宮 秀次<sup>†††</sup> 西川 博昭<sup>†††</sup>

Self-Timed Pipeline with Fine Grain Power Gating and Its Evaluation Kei MIYAGI<sup>†a)</sup>, Makoto IWATA<sup>††</sup>, Shuji SANNOMIYA<sup>†††</sup>, and Hiroaki NISHIKAWA<sup>†††</sup>

あらまし 本論文は,真に情報処理中の回路にのみ電力消費が極限される自己同期型パイプライン STP (Self-Timed Pipeline) におけるパイプライン段単位の細粒度パワーゲーティング機構の実装法とその評価について述べている。STP は,大域的なクロックを必要とせずに,隣接するパイプライン段間でのみデータ転送制御信号を授受して動作する自律的なパイプラインであるため,アクティブでないパイプライン段ではスイッチング電力を全く消費しない。本研究は,この STP の転送信号を活用して,必要最小限の追加回路で自律的な細粒度パワーゲーティングを実現することによって,リーク電力削減も同時に達成するものである。提案機構を備えた40 段の環状 STP パイプライン LSI チップを e-shuttle 65nm で試作し,通信処理の大部分を占める待機時を想定した実測評価を行った。その結果,パワーゲーティング機構を備えていない STP 回路と比較して,待機時電力を約 26%削減できることを確認した。これによって,本来ダイナミック電力に関して省電力である STP を更に超低消費電力化できる技術の確立に見通しが得られた。

キーワード 自己同期型パイプライン、省電力システム、リーク電力、実時間細粒度パワーゲーティング

# 1. まえがき

筆者らは、インターネットなどのトラヒックの指数 関数的増加をみれば、ネットワーキングシステムの省 電力化が必須になると着想し、超低消費電力化データ 駆動ネットワーキングシステム ULP-DDNS (Ultra-Low-Power Data-Driven Networking System) の研 究プロジェクトを進めてきた  $[1]\sim[3]$ .

本論文は、この ULP-DDNS の LSI 実現法として 着目した自己同期型パイプライン STP (self-timed pipeline) 回路 [4], [5] の省電力化技術について述べて いる. STP では、隣接するパイプライン段間でのみ データ転送制御信号を授受することによって、動作す る必要のあるパイプライン段のみを駆動させるため、 データを保持していないパイプライン段のトランジス タは全く動作しない。よって、クロック同期回路で一 般に用いられているクロックゲーティングのような付 加的な回路がなくとも、ダイナミック電力に関しては 省電力であるという特長がある。

一方で、LSI 製造プロセスルールの微細化に伴い、 リーク電力の増大が顕著になっており、通信時以外の 待機時の電力を削減する技術の確立も重要になりつつ ある. よって、本研究では、STP 回路における転送制 御信号を活用して、パイプライン段単位で自律的にパ ワーゲーティング PG (Power Gating) を実現する回 路[6] を考案し、STP の更なる省電力化を目指した. 一般に商用の LSI システムで用いられている PG 技術 は、LSI 全体ないしはプロセッサコア単位といった大 規模な回路に対して適用されている. これは、PG対 象の回路を細かくすると、それぞれの回路に、パワー ゲーティング用回路を個別に追加する必要があり,面 積オーバヘッドすなわち電力オーバヘッドが増大する ためである. また、電源オン時の突入電流に伴うノイ ズの影響を避けるために、ウェイクアップ時間を数 μs 以上に設定する必要がある. これらのことから, 回路

<sup>†</sup> 沖縄工業高等専門学校,名護市

Okinawa National College of Technology, Nago-shi, 905–2192 Japan

<sup>††</sup> 高知工科大学, 香美市

Kochi University of Technology, Kami-shi, 782-8502 Japan ††† 筑波大学,つくば市

University of Tsukuba, Tsukuba-shi, 305–8577 Japan

a) E-mail: k.miyagi@okinawa-ct.ac.jp

規模的にも時間的にも細かな電源制御ができないため, リーク電力削減効果がそれほど高くない.

自己同期型パイプラインを含む非同期回路を対象に した細粒度 PG 技術に関しては、m-out-of-n 符号に基 づく非同期回路を対象にした方式[7]や自己同期型パ イプラインを対象にした方式 [6], [8] がある. 前者の方 式は、ロジック回路内の信号遅延の変動に対する耐性 を備えた非同期回路であり、スペーサなどによりデー タ間を区分するために冗長な信号遷移が必要となる. 後者の方式は、遅延耐性は劣るが冗長な信号遷移がな いため, 前述したようにスイッチング電力を必要最小 限に抑えられる.しかし,文献[6],[8]では,いずれも 配置配線前のトランジスタネットリストを対象とした 提案に留まっており、LSI 実装上の技術的な課題が明 らかにされていない. すなわち,パイプライン段単位 の細粒度 PG においては、電源接続/遮断後の過渡的 な電流が相対的に大きくなり, 配線の寄生容量成分も 無視できないと考えられる.

以下,本論文では,STP 回路の特長を活用すれば,必要最小限の追加回路でパイプライン段単位の細粒度 PG を実現でき,かつ,時間的にも細かくリーク電力を削減できることを述べる.更に,通信処理の大部分を占める待機時を想定した上で,過渡的な電力を含めてリーク電力の削減効果を最大化できる,PG 回路の最適化設計法に関して議論する.その後,e-shuttle 65nm CMOS プロセスを利用して試作したテストチップの実測結果を通して,本提案方式の有効性を定量的に示す.

## 2. STP における細粒度 PG

本章では、まず STP の基本構成について述べ、その自律的な動作様式を活用すれば、必要最低限の追加回路でパイプライン段単位の細粒度パワーゲーティングを実現可能なことを示す.

## 2.1 自己同期型パイプライン STP

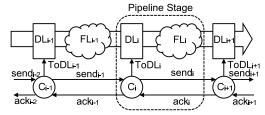

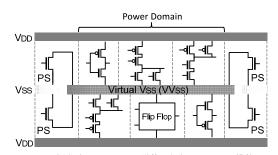

STP は基本的には図 1 のように構成される. 各パイプライン段は、パイプラインレジスタとして動作するデータラッチ DL (Data Latch)、処理回路 FL (Function Logic)、及び、データ転送制御回路として動作する一致記憶フリップフロップ (Coincidence flip-flop: C素子)により構成される. データはタグ付きのパケット形式で取り扱われ、STP 内では各パケットはステージ間の制御信号 (send 信号、ack 信号)の伝達によって自律的に移動する. 図 2 に STP の信号

DL : Data Latch FL : Function Logic C : Transfer Control Circuit

図 1 自己同期型パイプライン STP の基本構成 Fig. 1 Basic structure of self-timed pipeline.

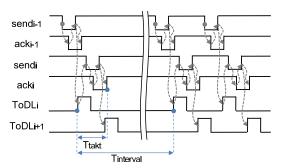

図 2 自己同期型パイプライン STP のタイミング図 Fig. 2 Timing chart of self-timed pipeline.

遷移を示す. 具体的には、まず、リセット時に全ての send 信号と ack 信号を 1、ToDL 信号を 0 にしてリセットを終える. パケットを転送するために、

- (1) (パケットの転送開始) C 素子  $C_{i-1}$  が前方段  $\sim \operatorname{send}_{i-1}$  信号を伝達する  $(\operatorname{send}_{i-1}:1 \to 0)$ . 同時 c, データラッチ  $\operatorname{DL}_{i-1}$  が前方段へパケットを送信する.

- (2) (ハンドシェイク)  $C_i$  は  $send_{i-1}$  及び  $ack_i$  信号が到着すると  $(send_{i-1}, ack_i: 0 \rightarrow 1)$ , データラッチ  $DL_i$  を開ける  $(ToDL_i: 0 \rightarrow 1)$ . 結果, パケットが 前方段へ転送される.

- (3) (ack 信号遷移) 同時に C<sub>i</sub> は, ack<sub>i-1</sub> 信号を 後方段に伝達し (ack<sub>i-1</sub>:0→1), 後続パケットの転 送を許可するとともに,

- (4) (send 信号遷移) send<sub>i</sub> 信号を前方段へ伝達 し (send<sub>i</sub>:1 $\rightarrow$ 0), 前方段へのパケット転送を開始 する.

- (5) パケットがある限り上記(1)~(4)を繰り返す. 以上のようなパイプライン段間の局所的な転送制御により, STPには, (a)局所的な信号伝達のみによって動作時にだけスイッチング電力を消費する省電力特性や, (b)供給電圧に応じて自律的に動作速度を可変で

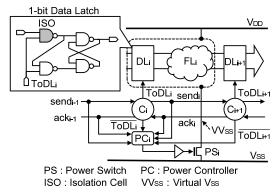

図 3 パイプライン段単位パワーゲーティング回路 Fig. 3 Stage-by-stage power gating circuit for STP.

きる特徴を利用した実時間電圧制御,更には (c) 負荷の変動に対する自律緩衝能力(エラスティック能力)といった,省電力 LSI 実現に適した特性がある [5]. STP 回路が本来有する最大スループット性能は,パイプライン段でのデータ転送にかかる最小時間であるタクト  $(T_{takt})$  の逆数で決まる。一方,プログラム実行時の実効スループット性能は,単位時間当たりに処理されるデータ数であるため,パイプライン段のデータ到着間隔( $T_{interval}$ )の逆数となる。

# **2.2** パイプライン段単位の細粒度パワーゲーティング

STP内のパイプライン段間で授受される send 信号と ack 信号は、当該ステージにおけるパケットの有無を表している。これらの信号を活用すれば、パイプライン段ごとに電力の供給/遮断を制御することが容易に可能になる。すなわち、動作していないステージの電源線をパワースイッチ PS(Power Switch)によりオン/オフすれば、プロセッサコア単位よりも細かなパイプライン段単位で無駄な漏れ電流を防ぐことが可能になる。図3にその回路図を示す。

パワースイッチ PS として、漏れ電流が比較的少ない、高しきい値 nMOS トランジスタを用い、これを処理回路とグラウンド線との間に挿入する。この PS を制御する回路 PC(Power Controller)は、当該段の前後の send/ack 信号と転送制御回路 C の内部信号を入力とする 6 入力 NAND ゲートのみで簡単に構成できる。以上の回路を各パイプライン段に付加することによって、パイプライン段単位の PG が実現される。

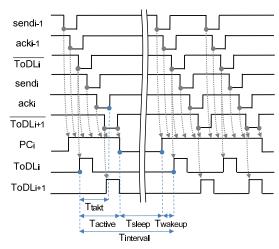

図 4 にこの回路の信号遷移を示す. 転送要求信号 send<sub>i-1</sub>, send<sub>i</sub>, 転送許可信号 ack<sub>i-1</sub>, ack<sub>i</sub>, DL 開

図 4 パイプライン段単位パワーゲーティングのタイミン グ図

Fig. 4 Timing chart of stage-by-stage power gating.

閉信号の否定  $\overline{\text{ToDL}_{i}}$ ,  $\overline{\text{ToDL}_{i+1}}$  のいずれかが 0 であれば、当該パイプライン段においてパケットが転送中(すなわち、処理中)であるため、その間は PS をオンにして電源を供給する。それ以外の場合には、電源を遮断しスリープする。図中の右半分で示しているように、複数のパケットが連続的に転送処理される期間においては、PS はオフされず継続的にオンとなり、不要な PS のスイッチングを避けることも可能になる。

これらより、電源オンの時間を  $T_{active}$ , PS オンから DL 開閉信号を立ち上げるまでの時間(以下、ウェイクアップ時間)を  $T_{wakeup}$  とすると、スリープ時間( $T_{sleep}$ )は、 $T_{interval}$  から  $T_{active}$  と  $T_{wakeup}$  を差し引いた時間( $T_{sleep} = T_{interval} - T_{active} - T_{wakeup}$ )となる.

パイプライン段水準のように細かな領域を対象とした PG では、一般に、

- PS, PC, 及び, 分離セル ISO (isolation cell) の性能・電力オーバヘッド

- 電源オン時の突入電流に伴うノイズの影響をなるべく小さく抑えることが肝要である[9]. 前者の中で、PC 回路については上述したように NAND ゲートのみで実現可能である. また、ISO に関しては、電源遮断された回路ブロックから電源供給されている回路ブロックへ不安定な信号値が伝搬して回路が誤動作するのを防ぐことが目的である. STP では、図 2 に示すように、データラッチ回路の一部が ISO の機能を

果たすことができるため、分離セル専用の追加回路が不要になり、電力的にも性能的にもオーバヘッドが生じないという利点がある。一方、PSに関しては、後述する実装において、性能・電力オーバヘッドを低減する工夫が必要になる。

後者に関しては、STP では各パイプライン段の DL 開閉信号はクロックに同期していないため、複数のパイプライン段が全く同時に電源オンになる可能性が極めて低い、よって、電源オン時に発生する突入電流の発生が時間軸上で分散するため、クロック同期型パイプライン回路に比べてグラウンドバウンス・ノイズ [10], [11] の影響を軽減でき、結果的に、 $T_{wakeup}$  を短くできる.

以上のように、STPの特長を活用すればパイプライン段単位の細粒度 PG によって、原理的には、リーク電力削減効果を向上できる可能性があることが判る。しかしながら、実際には、電源オンとオフのためにはエネルギーが必要になり、それがオーバヘッドとなる。よって、電源遮断されているスリープ期間に削減できるエネルギーが、PGのエネルギーオーバヘッドを上回る必要がある。このためには、エネルギーオーバヘッドを低減すると同時に、スリープ期間に削減できるリーク電力を増やす実装上の工夫が必要になる。

# **3.** パイプライン段単位の細粒度 **PG** の実 装法

本研究では、パワーゲーティング PG に伴うエネルギーオーバヘッドに対して、削減可能なリーク電力量が等しくなるスリープ時間  $T_{sleep}$  を、損益分岐スリープ時間 BEST(Break-even sleep time)と呼ぶ。本章ではまず、細粒度 PG の電力モデルとして、電源接続/遮断後の過渡的な電力を含めた BEST を定義する。次に、これに基づく細粒度 PG の LSI 実装法として、PS 挿入に伴うエネルギーオーバーヘッドと性能劣化を低減するための実装法について述べ、これらを容易化できる LSI レイアウト設計法を示す。

#### 3.1 損益分岐スリープ時間 BEST

細粒度 PG においては、PS が1度オフになる時点から一定時間スリープして再び PS がオンになる過程において、BEST は、削減可能なリーク電力を分母、エネルギーオーバヘッドを分子として、次式で近似できる.

$$BEST = \frac{E_{PS}^S + E_{rush}^S + E_{PS}^L}{P_{active}^L - P_{sleep}^L} \tag{1}$$

ただし、E<sup>S</sup><sub>PS</sub> は PS 及び PS 駆動用バッファと電源 制御用回路 PC のスイッチング電力量, Erush は電源 接続時の突入電流により消費するスイッチング電力量, ELs は当該パイプライン段が動作していない時間内に おける PS のリーク電力量を表す。また、 $P_{active}^{L}$  は電 源接続(PS オン)時, すなわちパワードメインと追 加回路のリーク電力である.  $P_{sleep}^{L}$  は,電源遮断 (PS オフ)時,すなわち PS, PS 駆動用バッファと PC の リーク電力である.  $P_{sleep}^{L}$  は, スリープ時間  $T_{sleep}$  が 経過すると徐々に0に漸近するため、プロセッサコア 単位 PG のように非常に長い Tsleep を仮定する場合, 0に近似されている[12].しかし、本提案のように細 粒度 PG を仮定すると無視できない項の一つである. 一方,  $E_{PS}^{S}$  に関しては、前章に述べたように、PC 回 路は NAND ゲートのみであるため、そのスイッチン グ電力量は 0 に近似でき、実質的には、PS 及び PS 駆動用バッファのスイッチング電力量と考えてよい.

式 (1) から判るように、細粒度 PG の実装上、調整の自由度が存在するのは、PS に関連するスイッチング電力量  $\mathbf{E}_{PS}^{\mathbf{S}}$  及びリーク電力  $\mathbf{E}_{PS}^{\mathbf{L}}$  である.

### 3.2 PS の省電力化

一般的なパワースイッチの設計手法として,文献 [13] では,PS オン時のドレイン電流  $I_{DS}$  と PS オフ時のリーク電流  $I_{OFF}$  の比率に基づく設計手法が述べられている.つまり, $I_{DS}$  を大きくすることで,PS の挿入による性能劣化を抑え,PS のリーク電流も小さくすることでリーク電力削減効果を高めて消費電力量の削減を図っている.しかし,この手法は,PS のスイッチング電力量  $E_{PS}^{S}$  までは考慮していない.これは,従来のコア単位 PG が,比較的長いスリープ時間  $T_{sleep}$  を対象に行われていたため,PS のスイッチング電力量がさほど問題にはならなかったためである.しかし,細粒度 PG では,電源オン/オフの頻度も高くなることが予想されるため, $E_{PS}^{S}$  の影響を無視することはできない.

そこで、本研究では、式 (1) の BEST より平均  $T_{sleep}$  が長く、かつ、 $T_{sleep}$  中の総消費電力量  $E_{total}$  を最小化できることを要件として、PS 用のセル設計を行った。 $E_{total}$  は、式 (1) 中のパラメタを用いて次式で表せる。

$$E_{total} = E_{PS}^{S} + E_{rush}^{S} + E_{PS}^{L} + \int_{0}^{T_{sleep}} \left( P_{active}^{L} - P_{sleep}^{L} \right) dt \quad (2)$$

## 3.3 PS による性能劣化の低減化

パワードメイン内の回路の動作速度が劣化する要因には,仮想グラウンド  $VV_{SS}$  の電圧上昇(IR ドロップ)がある.これは, $V_{SS}$  との間に挿入した PS の ON 抵抗や  $VV_{SS}$  の配線抵抗により,回路(DL,FL)と  $V_{SS}$  間の電流の流れを制限してしまうために生じる電圧上昇の一種である.特に,パワードメイン内にフリップフロップのような状態保持回路を含む場合には,IR ドロップで増加した遅延によってタイミング違反や,誤った信号を保持してしまう可能性があるため,その影響にとりわけ考慮しなければならない.文献 [14] では,IR ドロップの典型的な許容範囲として, $V_{DD}$  の 10%程度としている.しかし,微細化に伴う低電圧化や動的電圧制御技術との併用により,その許容範囲は狭まっていくことが予想される.

そこで、本研究では、回路動作時における  $VV_{SS}$  の IR ドロップが  $V_{DD}$  の 5%以下となるよう設計制約を設けた。また、低電圧時の PG を可能とするために、PS には、一般に用いられる高しきい値トランジスタではなく、標準的なしきい値(Standard Vth)のトランジスタを用いた。しかし、低電圧化が可能になる反面、その副作用によりパワースイッチのサブスレッショルド・リーク電流は増加する。その影響を抑制する手段として、ゲート長 L をある程度長くすることが考えられる。それにより、短チャネル効果を抑制できるため、サブスレッショルドリーク電流を低減できる。しかし、その場合、PS-on 時の  $I_{DS}$  特性が劣化する。すなわち PS の ON 抵抗が大きくなるため、その影響を補うためにゲート幅 W も同様に広くするよう設計した。

#### 3.4 LSI レイアウト設計

従来のプロセッサコア等を対象とした粗粒度 PGでは、PG 対象回路の周囲に仮想  $V_{DD}$  用の電源リングを設け、 $V_{DD}$  との間に複数の PS を配置して電源のオン/オフを制御している。したがって、電源接続時に発生する突入電流に起因するグラウンドバウンス・ノイズが PG 実装の一つの課題となっていた。その影響を抑制するためには、PS をオンにするタイミングを時間的にずらしながら突入電流のピーク値を抑制するディジーチェイン方式等を用いる必要があり、ウェイクアップには数マイクロ秒の時間を要していた [15]、そのため、従来のコア単位 PG では、数マイクロ秒以下のスリープ時間  $T_{sleep}$  に対しては PG することができない。

図 5 標準論理セル・ロウ単位の仮想グラウンド構築 Fig. 5 Virtual ground realized in each standard logic cell row.

本研究では、ナノ秒オーダの高速なウェイクアップを目標としているため、複数の標準論理セルを対象にして、ロウ単位で PG を行うレイアウト設計を行った。図 5 にその構成を示す。本レイアウトでは、前節までに議論した PS 用トランジスタを VVss と Vss に接続した PS セルを設計し、セルロウの両端にこの PS セルを配置している。このようなレイアウト設計を採用すれば、ASIC ベンダーから提供されているスタンダードセルをそのまま用いることができる。また、通常の配線とは別に VVss を配線する領域を有しているため、VVss の最下位層での配線が可能となる。したがって、文献 [16] で提案されている VVss の領域を余分に確保する構成法と比較して、配線混雑を抑制できると同時に、配線抵抗に起因する性能劣化と面積オーバーヘッドも抑制できる。

#### 4. LSI 実装と評価

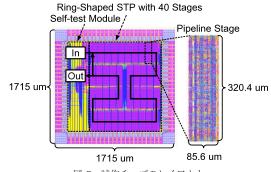

本章では、パイプライン段単位パワーゲーティングの省電力効果を定量的に示すために、e-shuttle 65nm 12 層メタル CMOS プロセスを用いて LSI チップを試作した結果及びその評価結果について述べる.

試作 LSI チップには、パイプライン段単位の細粒度 PG 機構を備えた 40 段環状 STP を実装した.各パイプライン段の処理回路 FLには、論理ゲートのスイッチング確率が比較的高いグレイコード生成器 (24×8bit) を実装し、各段で異なる値のデータが転送されるように工夫した.これらの回路の実装には、標準論理セルライブラリのうち比較的リーク電力が大きい低しきい値版 (CS202SZ) を用いた.これは、試作チップの実測において、リーク電流が微小な場合、基板上のノイズに紛れてしまい測定困難になる恐れがあったためである.また、本試作では、確実に動作

できることを優先したため、標準セルライブラリ内で提供されている ISO セルを用いた. これは、ISO セルが、製造時のアンテナ効果による不良を低減するダイオードを搭載しており、誤動作のリスクを軽減できるためである. 回路の論理合成には Synopsys 社 Design Compiler を、配置配線には Cadence 社のSoCEncounter を用いた.

更に、リーク電力削減効果の評価では、文献 [2] に記載の平均待機時間が  $2\sim3\mu s$  である通信処理を実行したときの  $T_{\rm interval}$  (平均値 804ns) を設定して、リーク削減効果を評価した.

## 4.1 PS セルの設計と予備評価

チップ試作に先駆けて、レイアウトしたパイプライ ン段1段を対象にして、パワースイッチ PS のトレー ドオフの評価を行った. まず, デザイン規則の最小値 である L=60nm の nMOS トランジスタを基準として, L=80nm, L=100nm で構成される計 3 種類の PS セ ルを設計し、それぞれのトレードオフの関係を SPICE シミュレーションにより評価した. 各 PS のゲート幅 は、アクティブ時の最大瞬時電流に基づくサイジング を行い、それぞれ VVss の上昇が VDD の 5%以下と なるように設定している. このとき, 各ゲート幅 W は 349nm, 465nm, 581nm であった. また, 低電圧条件 下における評価を行うために、電源電圧  $V_{DD}$  は 0.7Vとした. これは、PSのゲート長を80nmとした場合に おいて、ワーストケースに基づく SPICE シミュレー ションの結果,動作可能であった最低電圧 0.65V に対 して約8%の電圧マージンを想定した値である.温度 条件は、実行時を想定して、75°Cとしている。その 他、シミュレーション条件としては、SPICE の計算精 度が最大となるようパラメータを設定し、レイアウト 後のデータから抽出した配線容量や抵抗等の寄生成分 情報も加味している.

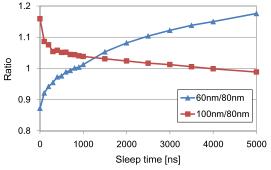

式 (2) に基づいて評価した結果の比を図 6 に示す。各プロットは、SPICE により算出したスリープ時間  $T_{sleep}$  ごとの電力量の比率をプロットしたものである。結果より、 $T_{sleep}$  が 786ns 以下であれば L=60nm、 $T_{sleep}$  が 786ns から 3889ns の範囲であれば L=80nm、3889ns 以上の  $T_{sleep}$  であれば L=100nm の PS セルが、式 (1) の BEST を満たした上で、式 (2) の総消費電力量を最小化できることが明らかとなった。したがって、対象とするアプリケーションの  $T_{sleep}$  の特性に応じて、この条件に合致するよう適切なサイズの PS セルを選定する必要がある。SPICE により算出した結

図 6 スリープ時の総消費電力量 (L=80nm で正規化) (0.7V, 75°C)

Fig. 6 Total energy ratio during sleep state (normalized).

表 1 損益分岐スリープ時間 BEST の予備評価 (0.7V, 75°C)

Table 1 Pblackesign evaluation of break-even sleep time (BEST).

| Gate size [nm]          | L=60    | L=80    | L=100 |

|-------------------------|---------|---------|-------|

|                         | W = 349 | W = 465 | W=581 |

| BEST [ns]               | 461     | 482     | 526   |

| Leakage power $[\mu W]$ | 4.588   | 3.364   | 3.249 |

| (PS オフ)                 |         |         |       |

| Switching energy [pJ]   | 2.804   | 3.225   | 3.749 |

果,ウェイクアップ時間( $T_{\rm wakeup}$ )は 873ps,  $T_{\rm takt}$ は 2.98ns,  $T_{\rm active}$ は 3.31ns であった。また、前述したとおり、 $T_{\rm interval}$ の平均値は 804ns であるため、平均的な  $T_{\rm sleep}$ は 800ns( $\approx$  804 - 3.31 - 0.873)となることから、L=80nm の PS セルが適している。また、L=60nm、L=80nm、L=100nm のそれぞれで評価した BEST 並びに、トレードオフの関係となる PS オフ時のリーク電力と PS のスイッチング電力量を表 1 に示す

L=80nm と L=100nm の PS セルに関しては、PS オフ時の定常状態のリーク電力がそれぞれ  $3.364\mu$ W と  $3.249\mu$ W であり、最大でも約 3%程度しかリーク電力に差がなかった。以上のことから、本研究では、L=80nm で設計した PS を用いて LSI 実装することにした。

#### 4.2 試作チップの実装と評価

本試作チップは、40 段環状 STP 全体の消費電力並びにパイプライン周回時間を観測できるように設計した。よって、式(1)、(2)で示した各パラメータは、実測で得られた総消費電力を、SPICEで得られた各パイプライン段の電力の比率で案分して求められる。試作チップのレイアウトを図7に示す。PS、PS 駆動用

図 7 試作チップのレイアウト Fig. 7 Prototype chip layout.

バッファ,及び,PCの面積オーバヘッドは,DLとFLの面積に対して、約29%であった.

環状 STP 内で、入力されたデータの合流と出力す るデータの分流を実現する専用のパイプライン段を除 いて、各パイプライン段は一様の構成とした、合流と 分流を行うそれぞれのパイプライン段の電力は SPICE で得られた電力の比率を用いて実測値を比例配分する ことにより算出する. 更に、その電力を引いた実測値 の残りをパイプライン段数 38 (= 40 - 2) で割ることで パイプライン段1段の消費電力を取得できるため、評 価が行いやすくなる. パイプライン構造は、演算資源 を再帰的に活用するための基本構成の一種である環状 とし、高いスループット性能を達成できるプロセッサ コアを想定して 40 段とした. 環状 STP では, データ (パケット) がパイプライン内を周回することが可能 となるため、スイッチング電力の実測もマルチメータ のサンプリングレートで可能になる. また, 回路が正 しく動作しているかを判別するセルフテストモジュー ルの電源線を独立にレイアウト設計し、40段の環状 STP のみの電力を実測可能とした. 更に, 試作 LSI を 搭載するボード上のレギュレータと 40 段の環状 STP の電源線との間に 0.1Ω のシャント抵抗を挿入するこ とで電力を実測可能にしている.

試作チップの諸元を表 2 に示す。本研究における LSI チップは,通信処理の大部分を占める待機時の電力削減を重視した通信処理向きプロセッサの事前検討として位置づけた。したがって,性能に関する制約条件として,文献 [2] に記載のデータ駆動プロセッサ ULP-CUE [3] の最大スループットの逆数である 3 ns を  $T_{takt}$  とした。40 段の環状 STP をデータが転送されるレイテンシの実測結果が 112ns であったことから,試作チップの  $T_{takt}$  は,3ns( $\approx 112/40$ ) を達成し

表 2 チップ諸元 Table 2 Chip specifications.

| Table 2 Only specifications. |                                          |  |  |  |

|------------------------------|------------------------------------------|--|--|--|

| Process                      | e-shuttle CS200L                         |  |  |  |

|                              | 65nm CMOS                                |  |  |  |

| Wiring (# of layers)         | 12 Metal                                 |  |  |  |

| Power-supply voltage         |                                          |  |  |  |

| Core                         | 1.2 V (Nominal)                          |  |  |  |

| I/O                          | 3.3 V (Nominal)                          |  |  |  |

| Threshold voltage            |                                          |  |  |  |

| Standard Vth                 | PMOS:-0.56 V (Condition *)               |  |  |  |

|                              | NMOS:0.60 V (Condition **)               |  |  |  |

| Low Vth                      | PMOS:-0.45 V (Condition *)               |  |  |  |

|                              | NMOS:0.50 V (Condition **)               |  |  |  |

| DL per stage                 | 192 bit                                  |  |  |  |

| FL per stage                 | 24 × 8 bit Gray-code generator           |  |  |  |

| # of PS per stage            | 688                                      |  |  |  |

| # of stage                   | 40                                       |  |  |  |

| Maximum transfer rate        | 795 M packet/sec. (1.2V)                 |  |  |  |

|                              | 230 M packet/sec. (0.7V)                 |  |  |  |

| Pipeline latency             | 28.4 nsec. (1.2V)                        |  |  |  |

|                              | 112 nsec. (0.7V)                         |  |  |  |

| Chip size                    | $2.1~\mathrm{mm} \times 2.1~\mathrm{mm}$ |  |  |  |

| Leakage per stage            |                                          |  |  |  |

| $1.2V, 25^{\circ}C$          | $25.3 \ \mu W \ (PS-on)$                 |  |  |  |

|                              | $2.28 \ \mu W \ (PS-off)$                |  |  |  |

| $1.2V, 75^{\circ}C$          | 128 μW (PS-on)                           |  |  |  |

|                              | $10.8 \ \mu W \ (PS-off)$                |  |  |  |

| $0.7V, 25^{\circ}C$          | $4.24 \ \mu W \ (PS-on)$                 |  |  |  |

|                              | $0.480 \ \mu W \ (PS-off)$               |  |  |  |

| $0.7V, 75^{\circ}C$          | $27.0 \ \mu W \ (PS-on)$                 |  |  |  |

|                              | $2.89 \ \mu W \ (PS-off)$                |  |  |  |

\*: L=60 nm, W=500 nm, Vds=-1.2 V, Vbs=0 V, Ids=-10  $\mu$ A, \*\*: L=60 nm, W=500 nm, Vds=1.2 V, Vbs=0 V, Ids=30  $\mu$ A (L: gate length, W: gate width, Vds: voltage between drain and source, Vbs: voltage between body and source, Ids: drain current)

ていることを確認した. PS オンと PS オフ時それぞれのリーク電力では、SPICE で取得した総リーク電力に占める ISO のリーク電力比を除いた環状 STP の電力比に実測した総リーク電力を乗算して求めることで、ISO のリーク電力を取り除いている. 結果より、PG (PS オフ) により、各温度条件でリーク電力を約11%に低減できており、典型的なしきい値の PS を用いても、省電力効果が得られることを確認した. また、パイプラインレイテンシと最大転送レートについても、SPICE で求めた ISO の遅延時間比に基づき、ISO の遅延時間を取り除いている.

## **4.2.1** 損益分岐スリープ時間 BEST の評価

試作チップの実測結果と SPICE で得られた電力の 比率を用いて、式 (1), (2) のパラメータを求め、パイ プライン段単位の細粒度 PG における BEST を算出し た. ただし、細かいスリープ時間  $T_{\rm sleep}$  ごとの  $E_{\rm rush}^{\rm S}$ の取得は、実チップからは困難であるため、SPICE シ

表 3 損益分岐スリープ時間 BEST の評価 (0.7V) Table 3 Evaluation of break-even sleep time (0.7V).

|          | 25°C | 75°C | 125°C |

|----------|------|------|-------|

| BEST[ns] | 1946 | 361  | 98    |

ミュレーションにより求めた、 $E_{PS}^S$  は、細粒度 PG を有効にして実測した電力から、無効にして実測した電力を引いた結果に、データが環状 STP を周回する時間を乗算して求めた。ISO による電力・性能オーバーヘッドは、SPICE で得られた ISO の電力の比率を用いて、実測値より取り除いた。PC 回路は全体に占める回路規模の割合が 0.1%以下であったため、その影響は無視できる。 $(P_{active}^L - P_{sleep}^L)$  と  $P_{PS}^L$  は、表 2 で得られた PS オン時と PS オフ時の結果を用いている。

0.7V の条件で評価した BEST を表 3 に示す。前述した平均的な  $T_{\rm sleep}$  が 800ns となる場合に, $75^{\circ}$ C 以上において,BEST  $< T_{\rm sleep}$  となり省電力効果が期待できる。

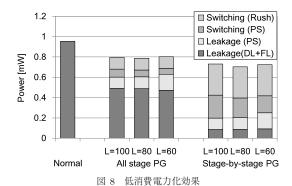

#### 4.2.2 省電力効果の評価

細粒度 PG 機構を備えた STP により実際にプロセッサを構成した場合に、削減可能な電力を見積もるために、文献 [2] に記載の通信処理をデータ駆動型プロセッサ ULP-CUE [3] 上で実行したときの実行プロファイルには、プロセッサを構成しているパイプライン段ごとのスリープ時間  $T_{sleep}$  が含まれている。これを式 (2) に代入すれば、当該パイプライン段の 1 回の  $T_{sleep}$  内の総消費電力量  $E_{total}$  が求まる。これらを全パイプライン段で全ての  $T_{sleep}$  について積算した結果を図 8 に示す。図 8では、通信処理における平均待機時間が  $2\mu$ s の場合の結果を示しており、また、比較のために、パワーゲーティング機構をもたない STP (normal) の電力、及び、パイプライン全体で PG を行った場合(All stage PG)の電力も示している。

PG の適用によってパイプライン単位パワーゲーティングでは,L=80nm の場合にリーク電力が 0.787mW で最小となり,パワーゲーティング回路をもたない STP に比べて,約 18%リーク電力を削減した.一方,パイプライン段単位 PG では L=80nm のときに 0.703mW まで低減されている.これは通常の STP 構成と比較して,リーク電力を 26%削減できており,細粒度化による省電力効果を確認した.また,パケットログを解析した結果,BEST の条件を満たす  $T_{sleep}$  は,全体の 34%程度であった.すなわち,BEST を満

Fig. 8 Evaluation result on power blackuction.

たさない  $T_{sleep}$  に対して、PG を抑制すれば、更なる省電力効果が期待できる。

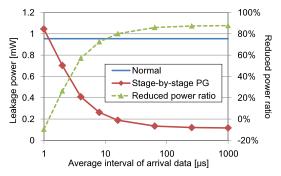

リーク電力削減効果は、性能要求と相反する関係に ある. つまり, 回路の最大スループット性能に対する 要求が緩和すれば、設計時にタクト Ttakt を長くでき るため、その分だけウェイクアップ時間  $T_{\text{wakeup}}$  を長 くでき、従って、よりゲート幅が小さいパワースイッ チPS を用いて電力オーバヘッドを抑えることにより、 リーク電力削減効果を向上させることができる. 逆 に、回路の最大スループット性能に対する要求が高く なると、削減効果は低下する、また、実効スループッ ト性能に関しては, 要求条件が緩和すれば, データ到 着間隔 T<sub>interval</sub> が長くなるとともに T<sub>sleep</sub> が長くな るため、削減効果が向上できる一方で、要求が高くな れば、削減効果は低下する. ここでは、性能要求に対 するリーク電力削減効果を評価するために,変更が可 能である通信処理の平均待機時間を変えたときの実行 プロファイルを用いてリーク電力削減効果を評価した 結果を図9に示す. 横軸は、要求される実効スルー プットによって変わる省電力効果を評価するために, データの平均待機時間をとっている. また, 縦軸左は パワーゲーティング機構をもつ場合 (Stage-by-stage PG) ともたない場合 (Normal) のそれぞれのリーク 電力を表しており、縦軸右は細粒度パワーゲーティン グにより削減されるリーク電力の割合を示している. 結果より、平均待機時間が 1µs の場合、電力オーバー ヘッドにより、電力が10%増加する.一方で、平均待 機時間が長くなるにつれて、リーク電力削減効果は高 くなり、1ms の場合には 88%削減できることを確認 した.

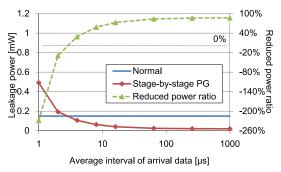

更に、25°C の条件での評価結果を図 10 に示す。この場合、トランジスタ自体のリーク電力が小さいため、

図 9 通信処理時のリーク電力削減効果 (0.7V, 75°C) Fig. 9 Reduced leakage power consumption during communication pressing (0.7V, 75°C).

図 10 通信処理時のリーク電力削減効果 (0.7V, 25°C) Fig. 10 Reduced leakage power consumption during communication prcessing (0.7V, 25°C).

リーク電力削減効果は低下する。平均待機時間が  $1\mu$ s のときには逆に 228%電力が増加する。一方で、平均待機時間が 1ms の場合には 87%削減でき、75° C 場合と同程度の削減効果が得られる。

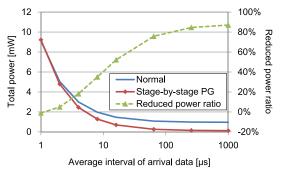

また、総消費電力に対するパイプライン段 PG の効果を示すために、75°C の条件において、通信処理全体の電力に対する電力削減効果を評価した。具体的には、実行プロファイルから取得したパイプライン段がアクティブになる回数に対して、電源オンの時間  $T_{active}$  に占める各パイプライン段のスイッチング電力量を乗じた結果の総和をとることで通信処理全体のスイッチング電力を見積もり、リーク電力との和をとることで通信処理全体に占める電力削減の割合を評価した。結果を図 11 に示す。この図より、細粒度パワーゲーティングにより、図 8 の条件(平均待機時間  $= 2\mu s$ )では総消費電力を $5\%削減できることを確認した。一方、平均待機時間が長くなるにつれて、<math>T_{active}$  の総スイッチング電力量が総リーク電力削減量に対して相対的に減るため、本提案方式による電力削減割合は向上する。

図 11 通信処理時の電力に占めるリーク電力削減効果 (0.7V, 75°C)

Fig. 11 Ratio of blackuced leakage power consumption to total power consumption.

## 5. む す び

自己同期型パイプライン STP は、隣接するパイプ ライン段間でのみデータ転送制御信号を授受するた め、アクティブでないパイプライン段では全くスイッ チング電力を消費しないという優れた特長をもってい る. 本論文では、STP の局所的なデータ転送制御信号 を活用した自律的なパワーゲーティング機構を実現す れば、アクティブでないパイプライン段のリーク電力 も削減でき, 更なる超低消費電力化が可能になること を述べた. 更に, e-shuttle 65nm CMOS プロセスで 提案回路を備えた STP 回路を LSI チップ実装し、通 信処理の大部分を占める待機時を想定した実測評価を 行った. その結果, パワーゲーティング機構を備えて いない STP 回路と比較して、待機時の総消費電力を 約26%低減できることを確認した.これによって、本 来ダイナミック電力に関して省電力である STP を更 に超低消費電力化できる技術の確立に一定の見通しが 得られたと考えている.

トランジスタのリーク電力は、製造プロセスのばらつきや動作温度によって変動するため、例えば、リークモニタ回路 [17] 等の情報に基づいて、パイプライン段ごとのパワーゲーティング機構にイネーブル信号を与えれば、より適応的に動作できる省電力システムを構成できると考えられる。また、要求性能や要求電力に応じて適切なしきい値の標準論理セルライブラリを選択するガイドラインも LSI 設計時には必要になると考えられる。これらに関しては、稿を改めて論じたい。

また、本論文で触れた試作 LSI チップは、超低消費電力化ネットワーキングシステムを実現するための

CREST 研究プロジェクトの一環として試作されたものでもあり、ネットワーキング方式、LSI プロセッサアーキテクチャ及びその LSI 回路実現法に至るまで省電力化を徹底することによって、総合的には従来システムに比較して、約 1/180 に低電力化できることも明らかになっている。その詳細については、文献 [2] を参照されたい。

謝辞 本研究の一部は、科学技術振興機構 JST CREST, 及び日本学術振興会科研費の支援を受けて行ったものである.

回路設計・シミュレーションは、東京大学大規模集積システム設計教育研究センターを通し、シノプシス株式会社及びケイデンス株式会社の協力で行われたものである.

#### 文 献

- [1] 三宮秀次,青木一浩,宮城 桂,岩田 誠,西川博昭, "超 低消費電力化データ駆動ネットワーキングプラットフォーム の試作,"信学論(D), vol.J96-D, no.10, pp.2319-2326, Oct. 2013.

- [2] 西川博昭,青木一浩,三宮秀次,宮城 桂,岩田 誠,宇津 圭祐,石井啓之,"超低消費電力化データ駆動ネットワーキ ングシステムとその評価,"信学論(B), vol.J96-B, no.6, pp.572-579, June 2013.

- [3] 三宮秀次,青木一浩,宮城 桂,岩田 誠,西川博昭, "超 低消費電力化データ駆動ネットワーキングプロセッサ ULP-CUE の試作とその評価,"情報処理学会論文誌 コンピュー ティングシステム (ACS), vol.6, no.1, pp.78–86, Jan. 2013.

- [4] K. Asada, H. Asano, S. Komori, S. Matsumoto, H. Miura, S. Miyata, H. Nishikawa, K. Shima, M. Shimizu, and H. Terada, "Coincidence element and a data transmission path," U.S. Patent 4 785 204, July 1986.

- [5] H. Terada, S. Miyata, and M. Iwata, "DDMP's: Self-timed super-pipelined data-driven multimedia processors," Proc. IEEE, vol.87, no.2, pp.282–296, Feb. 1999

- [6] K. Miyagi, S. Sannomiya, K. Sakai, M. Iwata, and H. Nisikawa, "Autonomous power-supply control for ultra-low-power self-timed pipeline," Proc. 2008 Int'l Conf. Parallel and Distributed Processing Techniques and Applications, pp.704–709, Las Vegas, Nevada, U.S.A., July 2008.

- [7] M. Imai, K. Takada, and T. Nanya, "Fine-grain leakage power reduction method for m-out-of-n encoded circuits using multi-threshold-voltage transistors," Proc. 15th IEEE Symp. Asynchronous Circuits and Systems, pp.209–216, Chapel Hill, North Carolina, U.S.A, May 2009.

- [8] 松本 敦,河野宇朗,鬼沢直哉,羽生貴弘,"制御情報共 有化に基づく非同期細粒度パワーゲーティング技術とそ

- のオンチップルータへの応用," 信学論(C), vol.J96-C, no.5, pp.73-84, May 2013.

- [9] H. Xu, R. Vemuri, and W.B. Jone, "Temporal and spatial idleness exploitation for optimal-grained leakage control," Proc. 2009 IEEE/ACM Int'l Conf. Computer-Aided Design, pp.468–473, San Jose, California, U.S.A., Nov. 2009.

- [10] K. Usami, T. Shirai, T. Hashida, H. Masuda, S. Takeda, M. Nakata, N. Seki, H. Amano, M. Namiki, M. Imai, M. Kondo, and H. Nakamura, "Design and implementation of fine-grain power gating with ground bounce suppression," Proc. 22nd IEEE Int'l Conf. VLSI Design, pp.381–386, New Delhi, India, Jan. 2009.

- [11] K. Kawasaki, T. Shiota, K. Nakayama, and A. Inoue, "A sub-μs wake-up time power gating technique with bypass power line for rush current support," Proc. 2008 IEEE Symp. VLSI Circuits, pp.146–147, Honolulu, Hawaii, U.S.A., June 2008.

- [12] J.H. Choi, Y. Xu, and T. Sakurai, "Statistical leakage current reduction in high-leakage environments using locality of block activation in time domain," IEEE J. Solid-State Circuits, vol.37, no.9, pp.1497–1503, Sept. 2004.

- [13] K. Shi and D. Howard, "Challenges in sleep transistor design and implementation in low-power designs," Proc. 43rd ACM/IEEE Design Automation Conf., pp.113–116, San Francisco, California, U.S.A., July 2006.

- [14] J.L. Coz, A. Valentian, P. Flatresse, and M. Belleville, "Power switch optimization and sizing in 65nm PD-SOI considering supply voltage noise," Proc. 2010 IEEE Int'l Conf. IC Design and Technology, pp.186–189, Grenoble, France, June 2010.

- [15] Y. Kanno, H. Mizuno, Y. Yasu, K. Hirose, Y. Shimazaki, T. Hoshi, Y. Miyairi, T. Ishii, T. Yamada, T. Irita, T. Hattori, K. Yanagisawa, and N. Irie, "Hierarchical power distribution with 20 power domains in 90-nm low-power multi-CPU processor," Proc. 2006 IEEE Int'l Conf., Solid-State Circuits Conf., pp.2200-2209, San Francisco, California, U.S.A., Feb. 2006.

- [16] 関 直臣、レイ ジャオ、小島 悠,池淵大輔、長谷川揚平、 大久保直昭、武田晴大、香嶋俊裕、白井利明、宇佐美公良、 砂田徹也、金井 遵、並木美太郎、近藤正章、中村 宏、 天野英晴、"MIPS R3000 プロセッサにおける細粒度動 的スリープ制御の実装と評価、"信学論(D)、vol.J93-D、 no.6、pp.920-930、June 2010.

- [17] C. Kim, K. Roy, S. Hsu, R. Krishnamurthy, and S. Borkar, "A process variation compensating technique with an on-die leakage current sensor for nanometer scale dynamic circuits," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol.14, no.6, pp.646-649, Nov. 2006.

(平成 25 年 10 月 23 日受付, 26 年 2 月 28 日再受付)

## 宮城 桂 (正員)

平 20 高知工科大・工・情報システム卒、 平 26 同大大学院博士課程了. 同年沖縄工 業高等専門学校情報通信システム助教, 現 在に至る. 博士 (工学). 自己同期型パイ プラインを用いた低消費電力 VLSI の研究 に従事.

# 岩田 誠 (正員)

昭 61 阪大・工・電子卒. 平 3 同大大学院博士課程単位取得後退学. 同年阪大・工・助手, 平 9 高知工科大助教授, 平 14 同教授, 現在に至る. その間, 平 14 東北大・通研 IT21 センター客員助教授, 平 18~平21 同客員教授を兼務. 平 20 カリフォルニ

ア大学アーバイン校客員研究員.博士(工学).データ駆動パラダイムを核とした,ソフトウェア環境及び ULSI 向きアーキテクチャの研究に従事.情報処理学会,IEEE 各会員.

# 三宮 秀次 (正員)

平 14 高知工科大・工・情報システム卒、 平 18 高知工科大助手、平 19 同大大学院 博士課程単位取得後退学、平 22 筑波大助 教, 現在に至る。博士(工学)、低消費電力 化データ駆動プロセッサの研究に従事、情 報処理学会, IEEE 各会員。

# 西川 博昭 (正員)

昭51 阪大・工・電子卒、昭59 同大大学 院工学研究科博士課程了、工博、日本学術 振興会奨励研究員,阪大助手,講師,筑波 大助教授を経て,現在,筑波大システム情 報系教授,情報学群長兼務、平6年7月~ 7年8月,平9年11月~12月,平10年

4月~5月 MIT 招聘研究員,平10年3月~4月 USC 招聘教授. データ駆動型超分散システムとその仕様記述環境等の研究に従事.平15 IASTED Best Paper Award in the area of Processor Architecture in PDCS 2003,平19 PDPTA'07 Ten Best Paper Award,平22 WORLDCOMP2010 Outstanding Achievement Award,平23 WORLDCOMP2011 Best Paper Award 各受賞.情報処理学会会員,IEEE シニア会員.