# **Built-In Self-Test (BIST) Techniques for Data Converter in Analog and Mixed-Signal Circuits**

Jun YUAN

A dissertation submitted to Kochi University of Technology in partial fulfillment of the requirements for the degree of

**Doctor of Philosophy**

Graduate School of Engineering Kochi University of Technology Kochi, Japan

September 2012

### Abstract

The rapid development of Integrated Circuits (IC) fabrication technology and the advance of System-on-a-Chip (SoC) design technology have made it possible to integrate millions of transistors on a single chip including digital and analog components. These mixed-signal solutions are widely used in modern mobile and multimedia devices. However, the high integration density has limited the accessibility and observability of the internal components since the limited I/O pins. As a result, the traditional off-chip testing has become a major challenge for analog and mixed-signal circuits, especially for the analog blocks, which have a large number of performance parameters with a fluctuation range.

As a tool for digital verification and production testing, Built-In Self-Test (BIST) has attracted a lot of research attention for analog circuit testing by implementing both stimulus generator and response analyzer entirely on-chip. It reduces the tester complexity, eliminates the need for off-chip interfacing, and allows the device to be tested many times during the manufacturing cycle of the product. Conventionally, performance parameters were measured on-chip to test analog blocks, but this specification-based BIST techniques result in high-test costs due to the complex testing circuits and test time. Therefore, another structural test technique, fault-based BIST was proposed to detect the possible physical defects caused by the IC manufacturing process.

In a typical application of the mixed-signal system, the external analog signals are sensed and changed to digital representations by Analog-to-Digital Converter (ADC), after the digital signal processing, the digital data are translated to our inherently analog world again by Digital-to-Analog Converter (DAC). ADC and DAC are at the systems level, and they typically contain amplifiers, sample-and-hold circuits, low-pass filters, etc. This dissertation aims to design fault-based BIST techniques for the data converter system based on the divide-and-conquer strategy. Firstly, the data converter system is broken into different kinds of sub-circuits based on the structure. Then, for each sub-circuit, one or more unusual signals are employed as test stimuli to excite the faults injected into this circuit, meanwhile, one or more parameters of the circuit are observed

to determine the test result by comparing with their fault-free values. As a result, each sub-circuit can be tested by its own independent BIST technique based on its structure. Finally, these self-testable subsystems are combined to re-constitute the data converter system, but it is not a simple assembling process. On the same chip, the BIST circuits for one sub-circuit can be shared with other sub-circuit, and some BIST circuits can be replaced to only one circuit with the same functions. In addition, some fault-free original sub-circuits under test in the data converter can be used as BIST circuit for other sub-circuits. As a result, the BIST circuits for the whole data converter can be simplified and the test controlling of the sub-circuits is transferred to the high level test controller/bus generated by the digital block in the mixed-signal system. The high level test bus controls the whole testing procedure, and enables the BIST circuits to test some sub-circuits in their idle time in the system operation of the data converter.

Based on the above-mentioned divide-and-conquer strategies, this thesis presents three BIST techniques. The first proposed BIST technique is to test Operational Amplifiers (Op Amps) by checking the stable output of the transient response, then to improve the fault coverage for Op Amp testing, a two-step BIST scheme and its implementation were also proposed. The second proposed BIST technique is the resistance-matching based BIST technique for current-mode R-2R DAC. This is a re-constructing example of the divide-and-conquer strategy. The third proposed technique is the Common-Mode (CM) BIST technique for Fully-Differential (FD) Sample-and-Hold (S/H) circuits.

The proposed BIST techniques shows that based on the exciting of the unusual signals like transient signal and pulse, the fault-based BIST technique can be achieved by checking the outputs of the Circuit under Test (CUT). Then, the existing BIST techniques can be integrated into a compact test technique for the whole data converter through simplification and reconfiguration, and every sub-circuit can be well tested with their acceptable fault coverage. Also, the proposed BIST techniques do not cause significantly performance degradation by disconnecting the BIST circuits to the CUT when the data converter is under its normal operation.

### Acknowledgements

Firstly, the author would like to express his deepest gratitude to his advisor, Prof. Dr. Masayoshi TACHIBANA, for his valuable supervision, supports and encouragements throughout the past nearly three years, and to Prof. Dr. Seiken YANO, Katsushi IWASHITA, Dr. Yukio MITSUYMA, Prof. Dr. Keiichi SAKAI and Koji NONAKA for their valuable suggestions and discussions.

Then, the author wishes to acknowledge Prof. Lawrie HUNTER for his useful research writing classes and two-page system, and to Prof. Mikiko BAN, Ms. Sonoko FUKUDOME, Ms. Kimiko SAKAMOTO, Ms. Mari YAMSAKI, Ms. Rika FUKII, Ms. Mariko KUBO, Mr. Motoi YOSHIDA and Ms. Kimi KIYOOKA, members of International Relation Center, for their kind helps. The author also wishes to thank Kochi University of Technology for its Special Scholarship Program for PhD study, and to Prof. Katsuki MATSUMURA for his hospitality and financial support under Flying-Fish Scholarship.

Especially, the author would like to thank Prof. Chaoyang LI and Prof. Yongdong TAN for her encouraging and helping in research and life in Japan, and also tanks Ms. Yumi TAKEMURA, colleagues in LSI laboratory and all friends in Kochi for their useful technique sharing and assistance.

Finally, the author wishes to sincerely appreciate his parents and younger sister for their endless love, sacrifices and supports for past years, and all the persons who helped to finish this thesis.

V

## **Table of Contents**

| List of Fi | gures                                                       | VIII          |

|------------|-------------------------------------------------------------|---------------|

| List of Ta | bles                                                        | XI            |

| Chapter    | 1. Introduction                                             | 1             |

| 1.1.       | IC Testing                                                  | 1             |

| 1.2.       | DFT and BIST Techniques                                     | 3             |

| 1.2.1      | Digital DFT and BIST Techniques                             | 3             |

| 1.2.2      | Analog and Mixed-Signal DFT and BIST Techniques             | 5             |

| 1.2.3      | Existing BIST Approaches for Analog Circuits                | 7             |

| 1.3.       | Fault Modeling for Analog Circuits                          | 8             |

| 1.4.       | Dissertation Developments and Organizations                 |               |

| 1.4.1      | . Motivation and Objectives of This Work                    |               |

| 1.4.2      | . Thesis Organizations                                      |               |

| Chapter 2  | 2. BIST Techniques for Operational Amplifier                |               |

| 2.1.       | Reviews on Op Amp Testing                                   |               |

| 2.2.       | The Stable Output Value (SOV) Checking based BIST           |               |

| 2.2.1      | . Test Strategy and Technique                               |               |

| 2.2.2      | . The SOV Checking based Test System Implementation         |               |

| 2.2.3      | Simulation Results                                          |               |

| 2.2.4      | . Conclusions                                               |               |

| 2.3.       | A Two-Step BIST Technique for Op Amp                        |               |

| 2.3.1      | . The Two-Step Test Strategy                                |               |

| 2.3.2      | . The Two-Step Testing System and Its Implementation        |               |

| 2.3.3      | Simulation Results                                          |               |

| 2.3.4      | . Conclusion                                                |               |

| 2.4.       | Conclusions and Discussions                                 |               |

| Chapter 3  | 3. A Resistance-Matching based BIST Technique for Current-M | Iode R-2R DAC |

| •          |                                                             |               |

| 3.1.       | Introduction to DAC Testing ,,,,,,                          |               |

| 3.1.1      | -                                                           |               |

| 3.1.2      | -                                                           |               |

|            | Resistance-Matching Based Test Strategy                     |               |

|            | The Current-Mode R-2R DAC with DFT Circuits                 |               |

|            |                                                             |               |

| 3.4.      | Test         | System Implementation                                       | 49 |

|-----------|--------------|-------------------------------------------------------------|----|

| 3.4.      | 1.           | The Proposed BIST System                                    | 49 |

| 3.4.      | .2.          | Output Response Analyzer                                    | 50 |

| 3.4.      | .3.          | Control Logic                                               | 52 |

| 3.5.      | Sim          | ulation Results                                             | 53 |

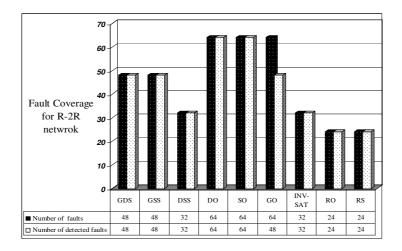

| 3.5.      | 1.           | Fault Modeling for R-2R DAC                                 | 53 |

| 3.5.      | .2.          | The Simulation Results and Discussion of the 8-bit R-2R DAC | 53 |

| 3.6.      | Con          | clusions                                                    | 60 |

| Chapte    | r <b>4</b> . | A CM BIST Technique for FD S/H Circuits                     |    |

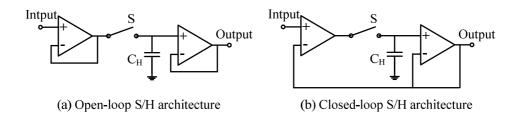

| 4.1.      | Intr         | oduction to S/H Circuit and Its Test                        | 62 |

| 4.1.      | 1.           | Charge Injection and Clock Feedthrough in Analog Switch     | 62 |

| 4.1.      | .2.          | S/H Circuits                                                | 64 |

| 4.1.      | .3.          | Overviews on S/H Circuit Testing                            | 68 |

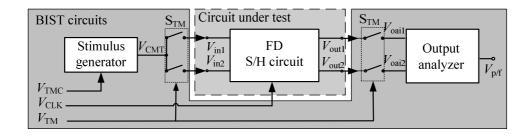

| 4.2.      | The          | CM Test Strategy                                            | 70 |

| 4.2.      | 1.           | FD Op Amp with CMFB                                         | 70 |

| 4.2.      | .2.          | CM Test for FD S/H Circuit                                  | 76 |

| 4.3.      | The          | CM Test System Implementation                               | 79 |

| 4.4.      | Sim          | ulation Results                                             | 83 |

| 4.4.      | 1.           | Fault Models for S/H Circuits                               | 83 |

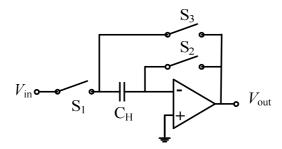

| 4.4.      | .2.          | The Simulation Results of the Flip-Around FD S/H Circuit    | 83 |

| 4.5.      | Con          | clusions                                                    | 86 |

| Chapte    | r 5.         | Conclusions and Discussions                                 |    |

| Referen   |              |                                                             | 91 |

| List of I | Publi        | cations                                                     |    |

|           |              |                                                             |    |

## **List of Figures**

| Figure 1.1  | Major steps in IC manufacturing flow [3]2                                           |

|-------------|-------------------------------------------------------------------------------------|

| Figure 1.2  | Basic BIST architecture [2]5                                                        |

| Figure 1.3  | Fault models for transistor: (a) GDS, (b) GSS, (c) DSS, (d) DO, (e) SO, (f) GO11    |

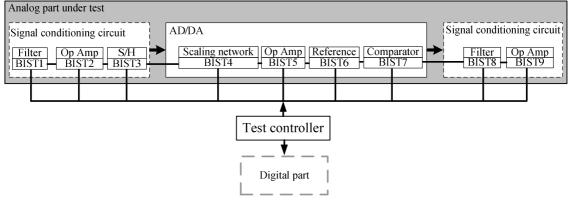

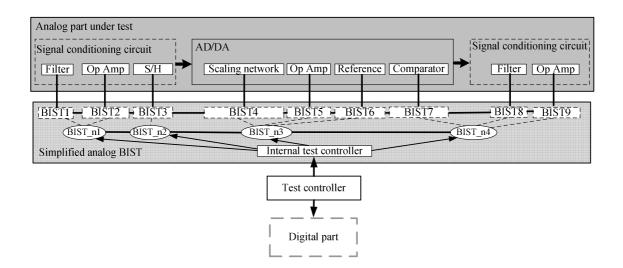

| Figure 1.4  | Architectures of system-level BIST and sub-circuit based BIST12                     |

| Figure 1.5  | The expected simplified sub-circuit-based BIST in this dissertation13               |

| Figure 2.1  | Transient responses of a voltage follower configured from the Op Amp18              |

| Figure 2.2  | Voltage follower configuration of an Op Amp19                                       |

| Figure 2.3  | The proposed SOV checking based BIST architecture: (a) The single Op Amp case.      |

| (b) The     | e multi-Op Amp case                                                                 |

| Figure 2.4  | The BIST circuit configuration: (a) A step signal generator. (b) A SOV checker20    |

| Figure 2.5  | (a) The checking regions of $WC1$ and $WC2$ . (b) Control and data signals settings |

| for test    |                                                                                     |

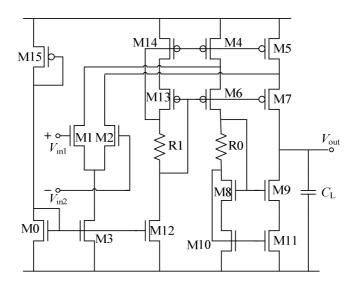

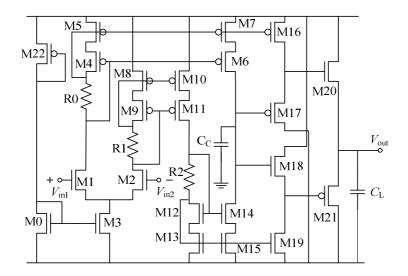

| Figure 2.6  | The circuit configuration of the two-stage Op Amp23                                 |

| Figure 2.7  | The circuit configuration of the folded-cascode Op Amp23                            |

| Figure 2.8  | The circuit configuration of the buffered Op Amp23                                  |

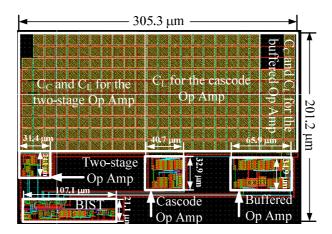

| Figure 2.9  | The layout pattern of the three Op Amps with the BIST circuits24                    |

| Figure 2.10 | The offset compensation for an Op Amp27                                             |

| Figure 2.11 | The output responses of the Op Amp under current-based comparator, voltage          |

| followe     | er and comparator configurations                                                    |

| Figure 2.12 | The proposed two-step BIST architecture                                             |

| Figure 2.13 | Output responses of the proposed two-step test scheme                               |

| Figure 2.14 | The test procedure of the proposed two-step test scheme                             |

| Figure 2.15 | The circuit configuration of the stimulus generators                                |

| Figure 2.16 | Block diagram of the designed response analyzer                                     |

| Figure 2.17 | The checking band of the two comparators                                            |

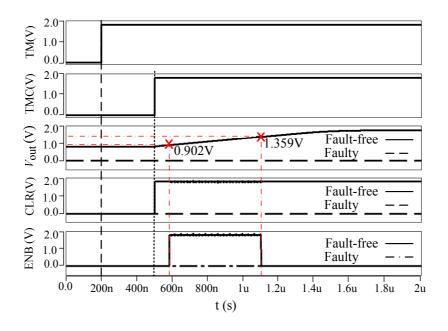

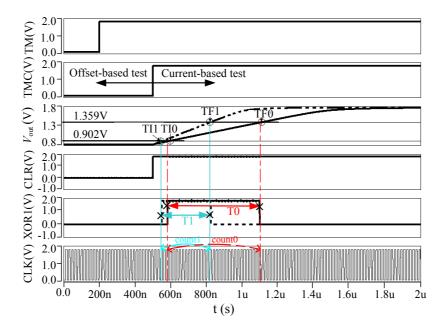

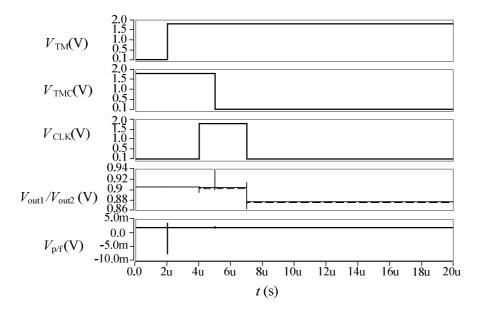

| Figure 2.18 | Timing waveforms of the BIST system operations                                      |

| Figure 2.19 | The slop detection in the current-based test stage                                  |

| Figure 2.20 | The circuit configuration of the two-stage Op Amp under test with inclusion of      |

| design      | for test                                                                            |

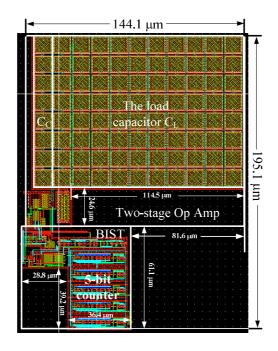

| Figure 2.21 | The layout pattern of the two-stage Op Amps with the BIST circuits                  |

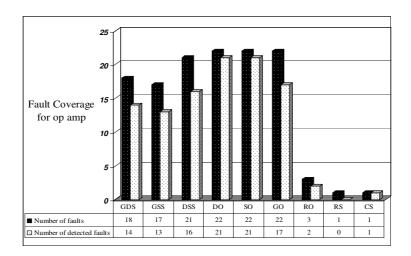

| Figure 2.22 | Faults simulation results                                                           |

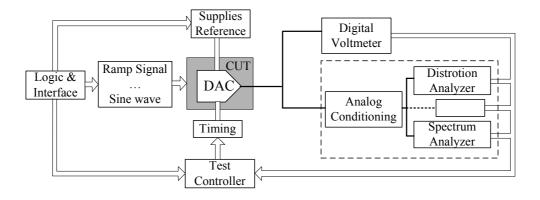

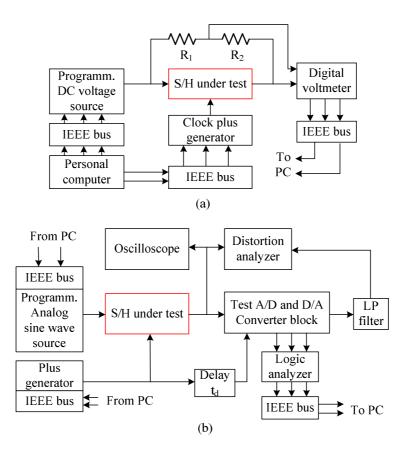

| Figure 3.1  | Basic setup for DAC testing41                                                       |

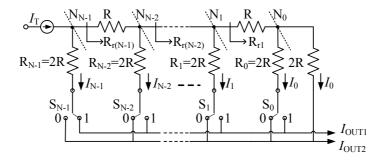

| Figure 3.2  | The R-2R ladder network                                                             |

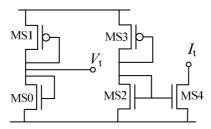

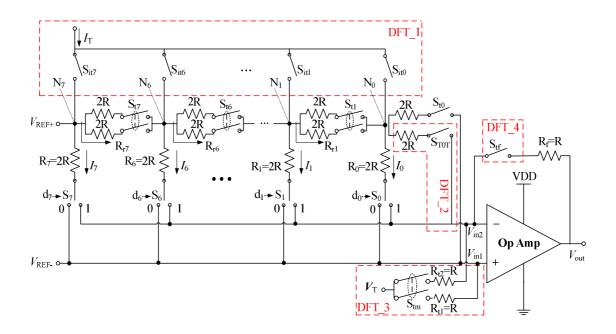

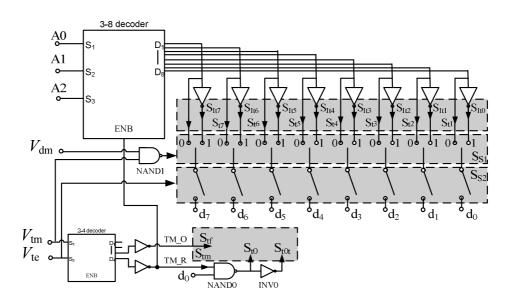

| Figure 3.3   | The circuit configuration of the current-mode R-2R DAC with DFTs46                       |

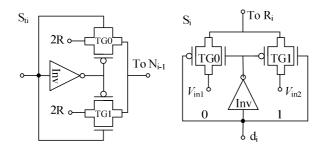

|--------------|------------------------------------------------------------------------------------------|

| Figure 3.4   | The circuit configuration of the switches S <sub>ti</sub> and S <sub>i</sub>             |

| Figure 3.5   | Two test types of R-2R network test mode: (a) Test configuration when the binary         |

| input is     | s set as " $10.00$ ". (b) Test configuration when the binary input is set as " $01.01$ " |

| Figure 3.6   | Test configuration for Op Amp used in the DAC under test                                 |

| Figure 3.7   | Block diagram of the BIST system for: (a) R-2R network test mode. (b)Op Amp              |

| test mo      | de49                                                                                     |

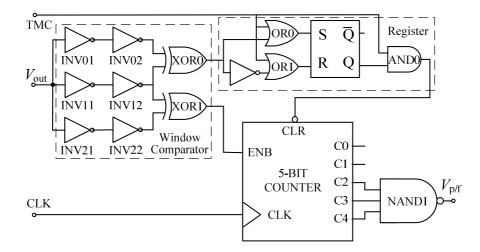

| Figure 3.8   | Output response analyzer: (a) The block diagram of the output response analyzer.         |

| (b) Cir      | cuit configuration of the window comparator                                              |

| Figure 3.9   | The internal test logic controller                                                       |

| Figure 3.10  | The controlling logic of the high level test bus                                         |

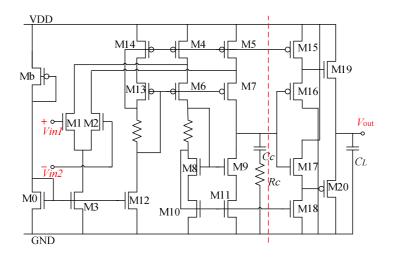

| Figure 3.11  | The circuit configuration of a buffered Op Amp54                                         |

| Figure 3.12  | Fault simulation results under R-2R network test mode                                    |

| Figure 3.13  | Fault simulation results under Op Amp test mode57                                        |

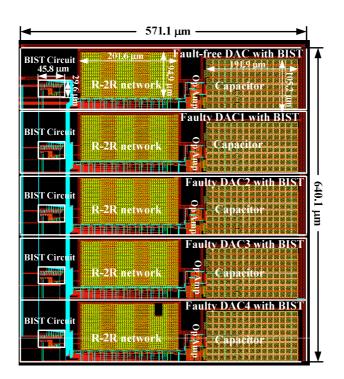

| Figure 3.14  | Layout patterns of the DUT with the BIST circuits                                        |

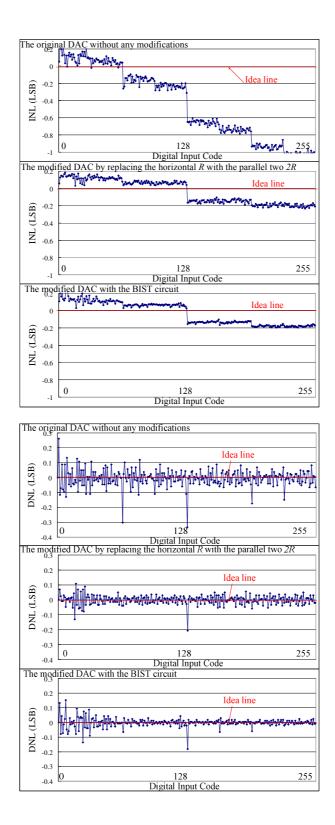

| Figure 3.15  | 5 INL and DNL comparisons of the general R-2R DAC, analog switches                       |

| injecte      | d/calibrated R-2R DAC and the proposed R-2R DAC with the BIST circuits59                 |

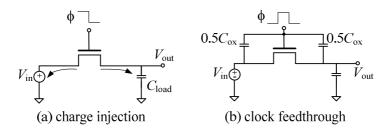

| Figure 4.1   | Illustration of charge injection and clock feedthrough using an nMOS switch [102].       |

| •••••        |                                                                                          |

| Figure 4.2 C | Conventional S/H architectures65                                                         |

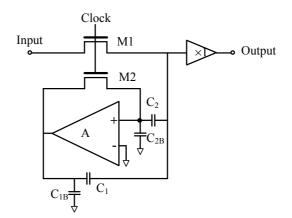

| Figure 4.3   | S/H circuit using Miller capacitance [120]66                                             |

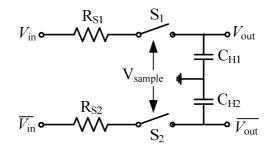

| Figure 4.4   | Basic differential S/H circuit [110]66                                                   |

| Figure 4.5   | Switched-capacitor S/H circuit [80]67                                                    |

| Figure 4.6   | Bottom plate sampling [102]67                                                            |

| Figure 4.7   | Test setup for S/H circuit [110]: (a) Testing DC characteristics. (b) Dynamic            |

| measur       | rements                                                                                  |

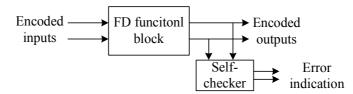

| Figure 4.8   | The general structure of self-checking [140, 141]69                                      |

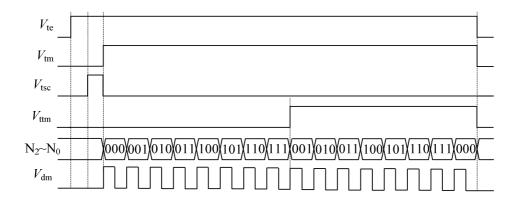

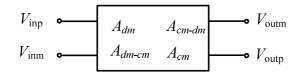

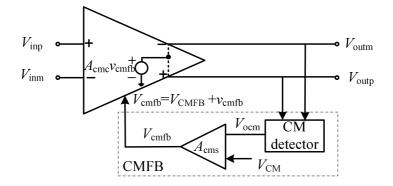

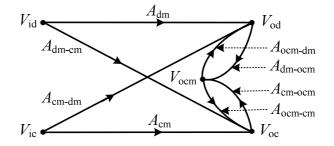

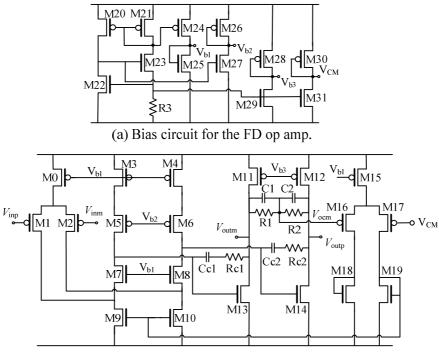

| Figure 4.9   | The typical architecture of the FD Op Amp70                                              |

| Figure 4.10  | The basic structure of a FD Op Amp with CMFB [77]72                                      |

| Figure 4.11  | Gain paths in the FD Op Amp with CMFB [150]73                                            |

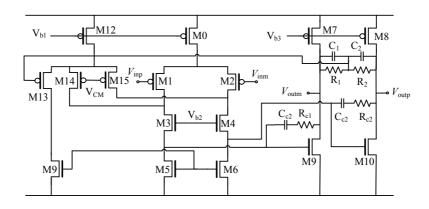

| Figure 4.12  | A two-stage balanced FD Op Amp [148]74                                                   |

| Figure 4.13  | A folded-cascode FD Op Amp74                                                             |

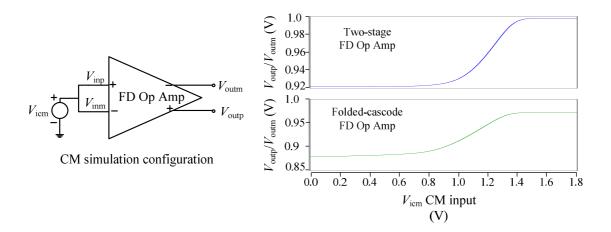

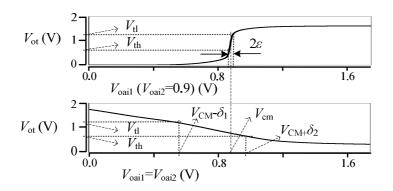

| Figure 4.14  | The CM input to CM output relationship of the two Op Amps76                              |

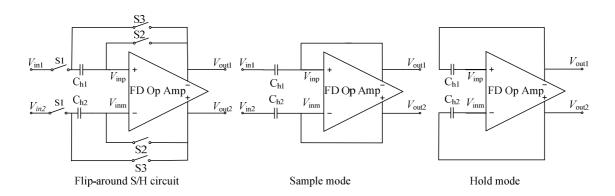

| Figure 4.15  | A flip-around S/H circuit and its operation modes76                                      |

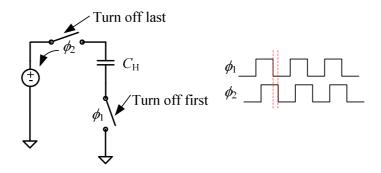

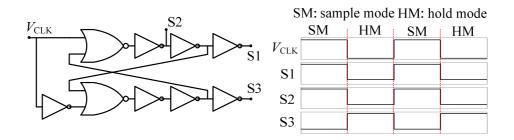

| Figure 4.16  | A non-overlapping two-phase clock generator and its timing waveforms77                   |

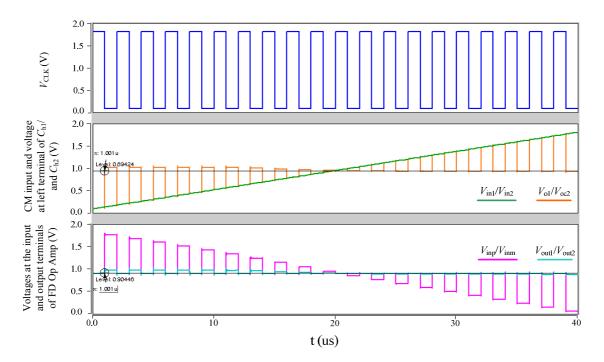

| Figure 4.17  | The CM simulation results of a FD S/H circuit78                                          |

| Figure 4.18 | The CM BIST setup for FD S/H circuit                                               |

|-------------|------------------------------------------------------------------------------------|

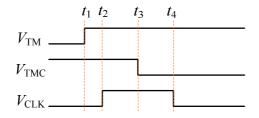

| Figure 4.19 | The timing waveforms for the CM test controlling signals80                         |

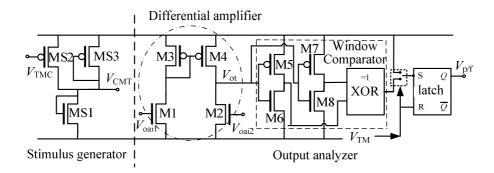

| Figure 4.20 | The designed BIST circuits for FD S/H circuit CM test81                            |

| Figure 4.21 | Voltage-transfer curves of the differential amplifier                              |

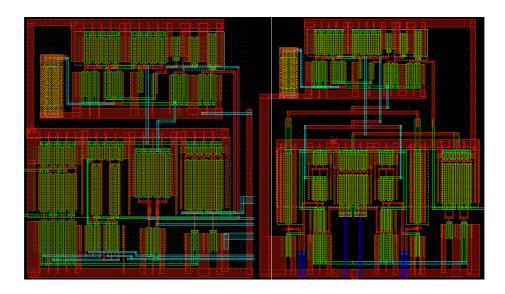

| Figure 4.22 | Two different layout patterns for the folded-cascode FD Op Amp84                   |

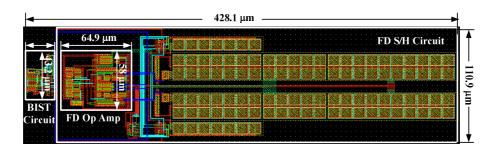

| Figure 4.23 | The layout pattern of the flip-around FD S/H circuit with the CM BIST circuits.    |

| ••••••      |                                                                                    |

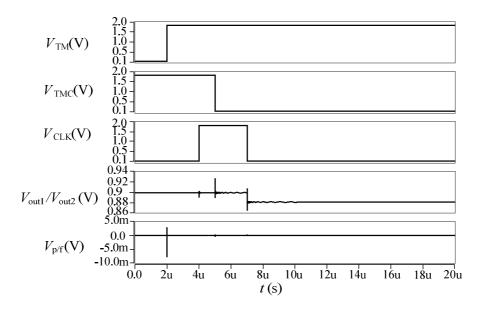

| Figure 4.24 | Fault-free CM simulation of the flip-around FD S/H circuit in schematic-level85    |

| Figure 4.25 | The fault-free CM simulation of the flip-around FD S/H circuit after the parasitic |

| extraction  | on form the physical design85                                                      |

|             |                                                                                    |

## **List of Tables**

| Existing test techniques for Op Amp15                                            |

|----------------------------------------------------------------------------------|

| Summary of elements parameters in the SOV checker shown in Fig. 2.4(b)20         |

| Summary of elements parameters of the three Op Amps24                            |

| Performance parameters of the original two-stage Op Amp and the two-stage Op     |

| with inclusion of the BIST circuit                                               |

| Performance parameters of the original folded-cascode Op Amp and the             |

| l-cascode Op Amp with inclusion of the BIST circuit25                            |

| Performance parameters of the original buffered Op Amp and the buffered Op Amp   |

| nclusion of the BIST circuit                                                     |

| The design of inverters used in window comparators                               |

| Summary of elements parameters for the two-stage Op Amp shown in Fig. $2.2035$   |

| Performance parameters of the original Op Amp and the Op Amp with BIST circuits. |

|                                                                                  |

|                                                                                  |

| Switch settings under different test modes                                       |

| Switch settings under different test modes                                       |

| -                                                                                |

| Summary of the elements parameters of the buffered Op Amp                        |

| Summary of the elements parameters of the buffered Op Amp                        |

| Summary of the elements parameters of the buffered Op Amp                        |

| Summary of the elements parameters of the buffered Op Amp                        |

| Summary of the elements parameters of the buffered Op Amp                        |

| 1                                                                                |

### Chapter 1. Introduction

The rapid development of IC fabrication technology and the advance of SoC design techniques have made it possible to integrate millions of transistors on a single chip including digital and analog components. As a result, the high integration density and the increasing complexity have limited the accessibility and observability to the internal component because of the limited I/O pins. Thus, the traditional off-chip test techniques have become more challenging for modern IC testing, and so new test techniques are required. Particularly, the analog part need be carefully tested.

This chapter begins with the introduction to IC testing during the production cycle. Then, the Built-In Self-Test (BIST) technique is described, and some hot issues are also presented for its application in the mixed-signal LSI systems. The existing BIST techniques are also reviewed. After this, the objective of this dissertation is included. Finally, the thesis structure is given.

#### 1.1. IC Testing

The typical IC design begins with the specification definition from the customers' requirements including the functionality, the input/output pins, technology, etc. The next step is to decide the architecture of the design by the architecture engineers, and the whole system is usually constituted by several sub-systems. Then, the design engineers implement the sub systems from the system level to the gate level or transistor level base on the possible technology and constrains. After this, the IC layout engineers finish the physical implementation, converting the design into geometric representation, which is also called layout patterns. Following the layout mask extracted from the physical design, the IC design is finally fabricated on a silicon ship, packaged and shipped to market.

The testing is involved in the IC product life-cycle including the IC design phase, IC manufacturing phase and the system operation phase [1,2]. The initial testing is performed within the Computer-Aided Design (CAD) environment [3], during the design phase. The design can be described into different levels, such as architecture level, gate level, transistor level, and layout pattern, so the design verification is

performed to ensure every refined implementation of the design would perform the intended function described in its specification by removing the design errors [2].

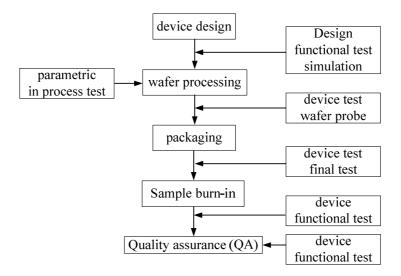

Next, the IC manufacturing testing is to detect the possible defects caused by the random process instabilities and contaminations during the IC manufacturing process. It mainly consists of wafer test, package test, and burn-in test, as illustrated in Fig. 1.1. First, the wafer test is to identify the faulty designs by probing sites on the wafer after the wafer processing. The test machine marks the faulty chips at the end of the wafer processing, and this information will be used in the next manufacturing step. Then, the wafer is cut apart, and the wafer test passed chips are selected for packaging. After the chips are packaged, testing is performed again to discard the faulty chips damaged during the packaging process. Wafer test and the package test seek to detect any defects that could have been sustained during the fabrication or packaging process. Finally, another important test step is burn-in or stress testing [2-4], where the ICs that passed the package testing are subjected to the high temperature and voltage to find the ICs that have marginal defects that will lead to "infant mortality" and low reliability [5]. Conventionally, additional testing is employed to assure the final quality before shipping to market or customers.

Figure 1.1 Major steps in IC manufacturing flow [3].

Finally, the "good" ICs are shipped to market and to be assembled on a Printed Circuit Board (PCB). The PCB fabrication process is a photolithographic process

similar some ways to the VLSI fabrication process [1], so the fabricated PCB should be tested as the IC manufacturing testing to discard the faulty ones. Then, the PCB are assembled with the ICs and retested to ensure it can perform as the requirement. The test about the PCB is usually called PCB test or board test. A general electronic system consists of more than one PCB, so the electronic system should be test again after the system is constituted. The electronic system passed the system test can finally put into service. During the system manufacturing process from the PCB to the final system in service, the IC chip would also be tested and the faulty ICs can be replaced by others.

IC testing addresses different issues at different phases. At the design verification phase, the test is to find the design errors in different design level, and then to modify the design to meet the specification. At the manufacturing phase, the test is to detect the physical defects that would happen during the manufacturing process, and discard the defective ICs. Also, the information like happening reason and lactation of the defects would be diagnosed and sent back to the design and production engineers to improve the IC design. At the system manufacturing and in the field service phase, the IC testing is to find the faulty ICs on the PCBs.

In the left part of this dissertation, the mentioned circuit test mainly indicates the IC testing in the IC manufacturing process and the fundamental objective of the testing is to distinguish between good and faulty ICs [6] during the manufacturing flow.

#### **1.2. DFT and BIST Techniques**

#### 1.2.1. Digital DFT and BIST Techniques

In the past, the design and test engineers were regarded as separate functions, and responsible for different parts of the IC products. The design engineers were to implement the ICs' required functions, and did not care about the ICs testing. After the IC manufacturing process, the test engineers controlled test devices to realize the IC testing. However, with rapid development of the fabrication technology, millions of transistors can be integrated in a single chip, so the limited controllability and observability of the ICs have become a bottleneck to test. As a result, the old approach can not keep up with the high integrality and complexity of modern ICs. Therefore, test engineers wish to bring the test thought and considerations into the design phase, to

improve the testability through some modifications. These modifications for test in the design phase are so-called Design-for-Testability (DFT, also DfT) [1,2,7,8] techniques, which were described as

"The collection of techniques that comprise design for testability are, in some cases, general guidelines; in other cases, they are hard and fast design rules. Together they can be regarded as essentially as a menu of techniques, each with its associated cost of implementation and return on investment" by Williams and Parker [8].

DFT techniques are widely used in modern digital circuits and generally fall into one of the following three categories:

- (1) Ad-hoc techniques, are usually done by incorporating multiplexers internal to the CUT to create one or more test modes of operation in which the primary inputs and outputs provide access to/from the internal difficult-to-test circuits via the multiplexers [2].

- (2) Scan design techniques, are implemented by connecting selected storage elements of a design in multiple shift registers, called scan chain, to provide them with external access. Scan design accomplishes this task by replacing all selected storage elements with scan cells, each having one additional Scan Inputs (SI) port and on shared/additional Scan Output (SO) port. By connecting the SO port of one scan cell to the SI port of the next scan cell, one or more chains are created [1].

- (3) Built-In Self-Test (BIST) techniques. *The basic ideal of BIST, in its most form, is to design a circuit so that the circuit can test itself and determine whether it is fault-free or faulty, respectively*[2].

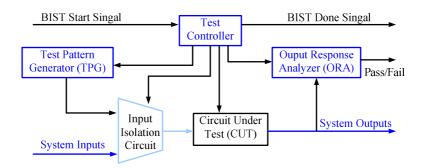

Testing typically consists of applying a set of test stimuli to the inputs of the Circuit under Test (CUT) while analyzing the output responses [1]. In the BIST application, the stimulus generation and output response analysis, implemented by the external test devices in the traditional off-chip test, are implemented by the BIST circuits incorporated into the CUT as shown in Fig. 1.2, so the circuit on-chip can access the internal signals much easier than the external tester, and the testability of the CUT can be improved using on-chip testing circuits. As it is shown in the blue parts in Fig. 1.2, the BIST circuits consist of three essential functions to facilitate the execution of the self-testing. The Test Pattern Generator (TPG) produces a set of test pattern to the

inputs of the CUT, and the outputs of the CUT are observed and analyzed by the Output Response Analyzer (ORA) to generate the test result of pass/fail indication. The test controller controls the whole test procedure with the BIST start and done signals to the high level test bus. Under the normal operation mode, the CUT performs the required functions described in the specification. Under test mode, the test controller or high test bus connects the BIST circuits to the CUT through the isolation circuits, and then execute the test.

Figure 1.2 Basic BIST architecture [2].

#### 1.2.2. Analog and Mixed-Signal DFT and BIST Techniques

With the testability improvement, modern digital circuits with high density and complexity can be well tested. However, another challenge has appeared with development of analog and mixed-signal circuits, the smaller analog blocks make these chips more sensitive to fabrication variations and tolerance accumulations [9], and the cost to produce mixed-signal devices is being dominated by their analog test costs [10]. Therefore, the design of analog blocks is often the bottleneck in the development of mixed analog-digital systems. While the analog section is usually limited to 5-10% of the mixed chip area, its design for test can take 80-90% of the develop time [7]. The test complexity and difference between analog and digital circuits described in [1,3,6,7,9-19] can be summarized as follow:

• Analog/Digital signals: analog signals are continuous in time and amplitude, while digital signals are discrete in both domains. Due to the continuous characteristic of analog signals, high accurate instruments are required to measure them, but the accuracy of analog instruments is limited by component variations over temperature changes, random differences between replaced components, and components drift over extended periods of time [3]. Also, the time and voltage continuous nature of their operation make them further susceptible to defects. Therefore, test procedures are needed to discriminate between various faulty conditions and the non-faulty condition [6]. As a result, for the analog circuit test, the measurement and analysis of the continuous signals make the fault signature be a main challenge. The simple comparing of digital outputs for fault signature can not be used in analog circuit testing.

- Input/Output relationships: in digital circuits, the relationship between input and output signals is Boolean in nature [6]. However, the input/output relationship of analog circuit is not simple Boolean, but complicated cause-effect relationship. To describe the performances of any analog circuit, many algebraic formulas are needed, so that the test simplification techniques in digital circuits can not be extended to analog circuits, and the traditional functional testing in analog circuit is costly. Also, the analytical techniques of Automatic Test Pattern Generation (ATPG) is difficult to applied to analog circuit testing, because the fault propagation and topological boundaries of the fault influence in analog circuits can not be well-defined as that in digital circuits.

- Sensitivity: the performance of analog circuit is sensitive to any changes like process variation and temperature, and also heavily depends on circuit parameters due to the nonlinearity of the analog devices. This property caused several problems for analog circuit testing. First, any modification to apply DFT technique would significantly degrade the performances of the CUT. Second, in digital case, its logic function is mainly susceptible to the defects causing catastrophic failures, and is essentially independent of device mismatches [10]. However, analog circuit is susceptible to all types of manufacturing errors and the main concern when using CMOS for an analog design is matching [20], so other defects that cause parametric change should also be considered in analog circuit. Limited functional verification does not ensure that the circuit is defect-free and escaped defects pose quality and reliability problems [6]. Additionally, the test quality would be decreased by the noise caused by the test devices in analog testing. The external cables between the tester and the chip introduce parasitic that affects test quality, expensive mixed-signal testers are

required to minimize circuit noise and improve on the measurement techniques [13].

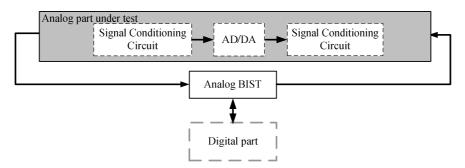

Based on the above mentioned challenges and differences between analog and digital circuits testing, the DFT techniques proposed for the digital circuits can not be directly applied to the analog circuits, some modifications need be made. In some cases, the ad-hoc technique used in digital circuit have been replaced by the CUT reconfiguration strategies [15,16,21-25] for testability improvement, because the direct replacement in analog would significantly degrade the performance of the CUT. The scan based DFT techniques used in digital circuits have also been changed to the mixed-signal test bus [26,27] by inserting data converting sections of ADC and DAC, and then the digital TPG and ORA can be used to implement analog circuit testing. The data converting sections should also be added in the analog BIST techniques for reusing the existing digital BIST techniques as shown in [2]. Another analog BIST technique has been proposed for the specific type of analog circuit. The analog test signals [28-30] are created by the on-chip stimuli generators to excite the CUT, and the analog ORA can directly observe the output response of the CUT and generate a digital test result. As a result, the data converting sections are no longer included in the BIST circuits, and that would eliminate the area overhead and design complexity. For specific analog circuit, specific test strategy is required to simplify the BIST circuits design, and this is the target that that will be reported in this dissertation.

#### **1.2.3.** Existing BIST Approaches for Analog Circuits

About analog circuit testing, there are two kinds of approaches: the first is specification-based testing, also called specification-oriented or functional testing, the functional specifications of CUT are measured and if any of the specification is violated, the circuit is declared faulty [31]. The specification-oriented testing tests every specification presented in the data sheet to determine the pass/failure of the circuit [1]. However, the specification-oriented testing has many drawbacks [32,33]. Typically, the specifications of analog circuits are insensitive to fluctuations in the manufacturing process, so the measurement errors would mask the effects of process variations. Also, the specifications of a circuit can be very complex, and so measuring them at various design corners to thoroughly test the circuit can lead to large testing times. The test hardware needed to measure the performance parameters of different circuits can be

quite different, forcing manufacturers to acquire different test equipment for different products [34].

The most basic analog functional measurement setup consists of a signal generator exciting the circuit-under-test with a known signal and an instrument to extract an appropriate parameter from the circuit's output response [10]. For BIST application, the analog test signal generator and the extract parameter extraction device should be replaced by on-chip circuits, and that would cause high area overhead. For this reason, according to the major cause of manufacturing defects, another test approach has been proposed, fault-based testing [15,35,36], is aimed at detecting manufacturing defects, which are modeled as faults. Unlike the specification parameters measurement in the specification-based testing, the fault-based testing approach is to analyze the structure of the CUT, and simulate it to determine the possible fault is existed or not. If any fault can be ascertained the CUT is faulty circuit. Conventionally, unusual signals are feed to excite the defects existing in the CUT, and the outputs are observed and compared with the expected outputs to determine the test result. According to the fault list, test engineers generates effective test signals to activate the fault in the circuit and the effect of the fault is propagated to the output, and outputs are observed and analyzed to determine the fault exists or not.

The performance measuring can also be used in fault-based testing. In this case, one or some of the performance parameters of the CUT is selected as measuring objective. If the change of the selected parameter caused by the injected faults into the CUT would be captured by the tester or on-chip test circuit, and that means the injected faults can be detected.

In fault-based testing, the fault coverage, which is the ration of the number of detected faults to the number of all faults, is commonly used to evaluate the proposed test technique or BIST technique.

#### **1.3.** Fault Modeling for Analog Circuits

For IC test, test engineers would not do research on real chip on the wafer or after package on which the real faults exist, because they cannot get the chip at the test design phase, and another reason is that they must predict the possible fault that may happen on the real chip and find test approach to test the possible faults before the circuit is manufactured. After the circuits are fabricated on a wafer, the design for test is used to determine the possible fault happened or not, and the fault model is the equivalent circuit of the real faulty part that may happen through the process line. Through the fault simulation, test engineers inject these equivalent circuits into the CUT, and then to evaluate the test patterns are effective or not. That is to say, fault models are used to represent the behaviors of the realistic fault in the circuit on wafer, and test engineers use fault simulation to measure the efficiency of their proposed test strategy, test pattern, test equipment or DFT techniques.

A fault is a representation of a defect reflecting a physical condition that causes a circuit to fail to perform in a required manner [1], and the abstraction process of the physical defects is also called as fault modeling, which is to find appropriate equivalent circuit to manifest the effect of the faults. Along the IC production line, photomasks are firstly extracted from the layout information of the circuit, and then the circuit is built on a wafer through the fabrication process according to the masks. Over the physical implementation process, physical defects may happen at every step. At photomask making step, a small localized region or spot is examined as point defect or spot defect which is the process less defect [34]. The point defect represents the material presence or absence that result in realistic physical defect at the structure level. Stacking faults, oxide pinholes, and extra or missing pieces of a conductor or semiconductor layer are all considered to be spot defects [37]. Another kind of defects that changes and degrades the performance parameter of the circuit would result from the fluctuation and variation of fabrication process, such as the diffusion time, temperature and so on. Some other examples of physical defects can be found in many works, such as high-resistive short in a metallization layer [15,38], gate oxide short [39], bridging defects, gate-oxide defects and open defects [40]. During the fault modeling the electrical effect of the physical defects are extracted and abstracted to a higher level to manifest the effect of the physical defect.

Based on the previous comment of physical defect, it is common practice to classify analog faults into two categories: catastrophic and parametric faults. Catastrophic faults, also referred to hard faults, are caused by random defects and cause short or open circuits or large-scale deviations of design parameters, like the aspect ratio of the MOS transistor [41]. If defects are sufficient to change the circuit schematics,

then they are classified as hard faults. If defects are too minor to cause hard faults, they are classified as parametric faults, also called soft fault. Soft faults can be further classified into parametric faults and deviation faults. Parametric faults are used to model the variation in the parameter that governs a device in the circuit of interest. Deviation faults refer to changes in the overall performance of the entire circuit of interest [1]. Hard faults and soft faults are not mutually exclusive. One fault may be classified as both a hard fault and a soft fault [1].

Many approaches have been proposed for fault modelling. According to modelling level, approximately three categories can be classified: schematic-based fault modelling, structural fault modelling and behavioural fault modelling. In [36], four levels of abstraction of the circuit are presented: process level, structure level, circuit level and logical level, so a defect can be translated to four levels. In process level, the mask is examined. In structural level, the fault modelling is based on the layout and the technology information of the fabrication process. After the effect extraction in structural level, defects can be mapped to circuit level based on the electrical effect. Finally, the behavior of the CUT with the defects can be simulated to create the behavior fault models based on the effect in the circuit level. This fault modelling process can be implemented by VLASIC [42] and the fault modeling approaches in [43-45] proposed based on the IFA [36]. However, this IFA based fault modelling is a time cost process, a circuit would have different fault lists due to the different layout patterns. Therefore the schematic-based [47-49] fault modelling was proposed to decrease the complexity and time cost of the defect-based fault modelling. The fault list can be directly created based on the schematic analysis of the CUT. In additional, sensitivity computation [50-52] was widely used in parametric fault modelling for analog and mixed-signal circuit.

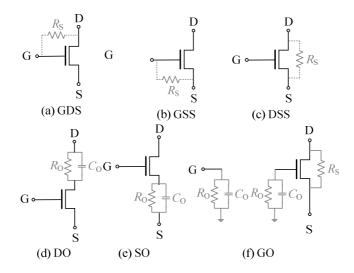

In this dissertation, due to catastrophic faults cover a wide range of realistic failures [53], so they are mainly considered including shorts and opens in MOS transistors, resistors and capacitors. Shorts were modeled by connecting a small resistor between each pair of terminals [54], including Gate-Drain Short (GDS), Gate-Source Short (GSS), Drain-Source Short (DSS), Resistor Short (RS) and Capacitor Short (CS). Opens were modeled by inserting a parallel combination of a large resistor and a small capacitor in series into each terminal [54], including Drain Open (DO), Source Open

(SO), Resistor Open (RO) and Capacitor Open (CO). Particularly, Gate Open (GO) was modeled by means of grounded parallel combination of a large resistor and a small capacitor at the two disconnecting terminals [54]. These catastrophic faults for an nMOS transistor are illustrated in Fig. 1.3. The injected short small and open large resistors were respectively set to  $100\Omega$  and  $100M\Omega$  with reference to case in [47], and the small capacitor injected in the open cases was set to 10fF. These values can be changed according to their characteristics, for example the small resistor injected in the short cases, were set to  $1\Omega$  in [55,56].

Figure 1.3 Fault models for transistor: (a) GDS, (b) GSS, (c) DSS, (d) DO, (e) SO, (f) GO.

#### **1.4.** Dissertation Developments and Organizations

#### 1.4.1. Motivation and Objectives of This Work

The above-mentioned BIST techniques in IC testing have led to the research and development of this dissertation. Although a large number of BIST techniques for circuits have been proposed, only a few of them have been implemented in real chip due the complicated on-chip test circuits, so the simple and compact BIST techniques with low cost are still needed, especially for recent advanced analog and mixed-signal circuits.

Most existing BIST techniques for analog and mixed-signal circuits are based on the specification measurement, which caused high design complexity of the BIST circuits and long test time. In the analog and mixed-signal testing, many techniques can not been directly extended to different analog and mixed-signal circuits since they have different structures and different performances, and specific analog circuit requires specific technique. Therefore, this dissertation is aim to get an insight into the fault-based BIST application in analog and mixed-signal systems with the referred fault models in Sect. 1.3, to the proposed effective feasible techniques for data converting systems based on their structural analysis.

For the data converting circuit, the widely used BIST strategy is to test the data converting system like a back-box as it is shown in Fig. 1.4(a), even though the data converting system consists of many circuits with different characteristics and functions. The analog BIST circuit generates test stimuli to the data converting circuit, and observes the outputs to determine the test result. However, this functional BIST strategy would cause low fault coverage due to the limited accessibility and observability, and mask some faults in the internal sub-circuits of the data converting circuit. Hence, the sub-circuit based BIST strategy was proposed and it is illustrated in Fig. 1.4(b). To improve the testability, the data converting circuit is broken into several sub-circuits like

(a) System level test archtechure.

(b) Subcircuit-based test archtechure.

Figure 1.4 Architectures of system-level BIST and sub-circuit based BIST.

filter, Op Amp, scaling network, S/H circuit, comparator or reference. Then, BIST strategies are proposed for each sub-circuit, so all sub-circuit can be tested by its own BIST circuit. However, this kind of divide-and-conquer would cause some problems like performance degradation and area over head, so this sub-circuit based BIST strategy need be improved with the benefit of high testability.

Some BIST circuits for different sub-circuits can be combined to decrease the cost as it is shown in Fig. 1.5, the *BIST1-BIST3* were combined to a new on-chip circuit  $BIST\_n1$ , which can also test the sub-circuits tested by *BIST1-BIST3*. Other new BIST circuits can be created in the same way. Similarly, the new BIST circuit can be recombined, and some sub-circuit under test can also be used to test other sub-circuit. The simplified analog BIST circuit is controlled by the designed internal controller to test all the sub-circuits in the data converting system, the sub-circuits used in Fig. 1.4(a) and Fig. 1.5 are just some examples, not the real configuration of the data converting system.

Additionally, all the designs in this work were implemented using Rohm 0.18  $\mu$ m CMOS technology provided by VLSI Design and Education Center (VDEC), which is located in the University of Tokyo and shared by users all over Japan.

Figure 1.5 The expected simplified sub-circuit-based BIST in this dissertation.

#### 1.4.2. Thesis Organizations

The left of this thesis is organized into four chapters. The following chapter 2 gives the proposed two BIST techniques for Operational Amplifiers (Op Amps). In the first approach, the Op Amp is reconfigured as a voltage follower to excite the possible

defects and the stable (desired) output voltage (SOV) of the transient response is analyzed by SOV checker to determine the test result. Then, In order to improve the fault coverage in Op Amp testing, a two-step BIST scheme and its implementation have also been proposed.

Chapter 3 presents a resistance-matching based BIST technique for current-mode R-2R DAC. This is a re-constructing example of the divide-and-conquer strategy. The SOV checking based test technique proposed in the first chapter was used to test the Op Amp in the R-2R network DAC, and then the resistance-matching based test strategy was employed to test the R-2R network based on the tested Op Amp.

Chapter 4 presents the Common-Mode (CM) BIST technique for Fully-Differential (FD) Sample-and-Hold (S/H) circuits, due to the FD topologies are commonly used to eliminate the clock feedthrough and charge injection to a first order in S/H circuits. The performance of the small CM gain in FD Op Amps is employed to test FD S/H circuits based on the CM setup in this study.

Chapter 5 finally gives the summarization of proposed BIST techniques for data converting circuits and discussions. In addition, the following research will be mentioned for the unfinished parts in the data converting systems.

# Chapter 2. BIST Techniques for Operational Amplifier

This chapter presents two fault-based BIST techniques for Op Amps, which are most frequently encountered parts in analog and mixed-signal LSI systems. Without any parameters modification, the BIST techniques based on the stable output value checking of the transient response can be applied to test all the Op Amps in the same analog and mixed-signal system, even the Op Amps are designed with different architectures. Then, to improve the fault coverage, a two-step BIST scheme and its implementation for Op Amp is presented. In addition to the catastrophic faults, the proposed technique can particularly detect the capacitance variation in the compensation capacitor by combining the current-based test with the offset-based test.

Firstly, the overviews of the existing test techniques for Op Amps are given. Then, the BIST techniques based on the stable output value checking of the transient response and the two-step scheme are presented. Finally, the conclusion is drawn.

#### 2.1. Reviews on Op Amp Testing

A variety of test techniques have been proposed for Op Amps, and they are summarized in Table 2.1.

|                     | Test Strategy                  | Works      | <b>BIST Implemented</b> |

|---------------------|--------------------------------|------------|-------------------------|

| Specification-based | Specification measurement      | [57-59]    | N/A                     |

|                     | Specification measurement      | [52,60-65] | [52,60]                 |

| Fault-based         | Oscillation-based              | [66-70]    | [69]                    |

|                     | Electronic variables of Op Amp | [71-74]    | [71-73]                 |

**Table 2.1** Existing test techniques for Op Amp.

The widely utilized scheme is based on the specification measurement [57-59]. In these cases, all the functional parameters of the Op Amp under test are measured and compared with the expected values to determine the test result. However, these specification-based BIST techniques require complex on-chip circuits to implement the specifications measurement that would cause high test cost, and also result in either excessive or insufficient testing.

The fault-based testing is widely accepted as an alternative to functional testing, and the proposed fault-based techniques for Op Amps can be classified into three categories. First, some functional parameters [52, 60-65] are still used in fault-based testing approaches to detect the possible faults. For example, the Op Amp under test was converted into a voltage follower in [60-62], and the transient response of the voltage follower was analyzed in order to measure the overshoot and slew rate deviation with respect to the fault-free response. However, the parameters of overshoot and slew rate vary among different Op Amps with different architectures, so the designed system must be modified to test other Op Amps, even in the same chip. In [52], an AC and DC compacted testing technique was presented by monitoring the amplitude and offset of voltage signals. However, a sinusoidal wave was employed as test stimulus, which made this technique infeasible for on-chip test since the complex sinusoidal wave generator.

Second, in the oscillation-based test techniques [66-70], the Op Amps under test were converted into an oscillator, and the reconfigured circuit parameters like oscillation frequency and power supply currents were evaluated to detect the possible faults in the Op Amps without any test stimulus. However, the measuring and analyzing circuits of oscillation frequency would be too complex.

Third, some electronic variables related to the Op Amp under test were monitored for fault signature signals. In  $I_{DDQ}$  testing techniques [71], the power supply current of the Op Amp under test was monitored by a current sensor in order to determine the current deviation caused by the defects, but it is hard to design a current sensor without performance degradation to the original amplifier. In [72] current signals were employed as test stimuli and injected in two nodes at the output stage of the Op Amp. In [73,74], the built-in DC test signals from the internal nodes were employed to detect the hard-detect fault to the voltage-based test, but the AC analysis on-chip circuit would cause complex circuit design for BIST application.

#### 2.2. The Stable Output Value (SOV) Checking based BIST

Some above-mentioned test techniques have been partially implemented in BIST application, and in some cases, extra test device is still needed to assist the AC analysis

or complex signal generation. Additionally, every Op Amp under test requires a specialized external testing circuit with respect to its parameters, even using the same BIST scheme. Thus, the Stable Output Value (SOV) checking based BIST is presented, and it can test all the Op Amps in a complex analog and mixed-signal system using only one fixed BIST circuit.

#### 2.2.1. Test Strategy and Technique

When a step signal inputs to the voltage follower converted from an Op Amp under test, the output of the voltage follower is called as transient response and it can be observed to measure the performance parameters [75,76] like slew rate, setting time, and phase margin.

The voltage follower configuration of an Op Amp is useful, and many parameters can be captured and calculated from the transient response. Therefore, transient response can be chosen as a monitoring subject to test Op Amp for its high information containing. As a fault happened, the parameter deviations of slew rate, setting time or phase margin can be reflected from the transient response distortion. Hence, the fault can be detected by observing the transient response.

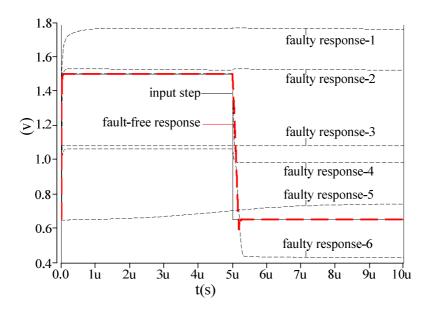

Figure 2.1 shows some examples of transient responses deviation with reference to the fault-free response. If the distortions of transient response can be extracted, the existing faults in the Op Amp under test can be easily detected. In work [60-62], parameters of slew rate and overshoot were chosen as test variables of deviation reflection to declare the transient response distortion. However, the faults, which caused transient response distortion like the faulty response-6, can not be detected by measuring slew rate and overshoot because the slew rate and overshoot variables did not deviate or was changed a little, but it can be detected by observing the SOV of the transient response.

The transient response finally rose or fell to a stable voltage value with a little propagation delay according to the input step signal, which skipped from an initial voltage to another stable voltage. For a fault-free Op Amp, the SOV should be equal to the final stable voltage of the input step signal. For this reason, the SOV is considered as an alterative test variable to test the Op Amp.

Figure 2.1 Transient responses of a voltage follower configured from the Op Amp.

With reasonable accuracy assuming, most Op Amps configurations can be modeled as a second-order system. The general second-order system in the frequency domain can be described as Eq. 2.1 [75]

$$A(S) = \frac{V_o(s)}{V_{in}(s)} = \pm \frac{A_0 \omega_n^2}{s^2 + 2\zeta \omega_n s + \omega_n^2} = \pm \frac{A_0 \omega_0^2}{s^2 + (\omega_0 \omega_0^2) s + \omega_0^2}$$

(2.1)

where

$A_0$  is the low-frequency gain,

$\omega_n = \omega_0$  is the pole frequency in radians per second,

$\zeta$  is the damping factor 1/(2Q), and Q is the pole.

Then, the Op Amp under test is converted to a voltage follower shown in Fig. 2.2, the general response to the step signal  $V_i$  in time domain can be written as

$$V_{o}(t) = A_{CL} \left[ 1 - \frac{1}{\sqrt{1 - \zeta^{2}}} e^{-\zeta \omega_{n} t} \sin\left(\sqrt{1 - \zeta^{2}} \omega_{n} t + \phi\right) \right] \bullet V_{i}(t)$$

(2.2)

where  $A_{CL} = \frac{A_0}{(A_0 + 1)}$  is the closed-loop gain.

Since the gain  $A_0$  is large enough for Op Amps and the term  $e^{-\zeta \omega_n t}$  would become

approximately zero with the time increase. After the transient response stabilized, Eq. 2.2 can be simplified as  $V_o(t) \approx V_i(t)$ , so the SOV is almost determined by the step input for a fault-free Op Amp, so only one fixed SOV observation BIST circuit can test all Op Amps in an analog and mixed-signal system using a single step input.

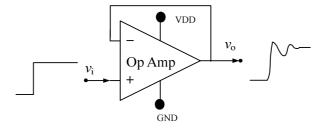

Figure 2.2 Voltage follower configuration of an Op Amp.

#### 2.2.2. The SOV Checking based Test System Implementation

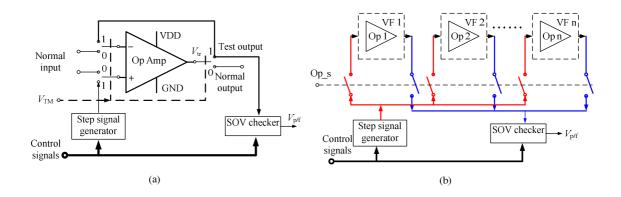

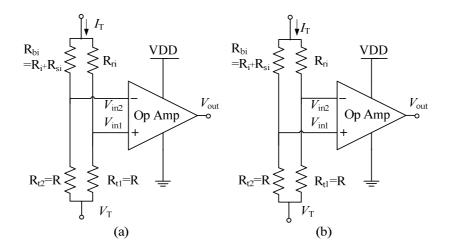

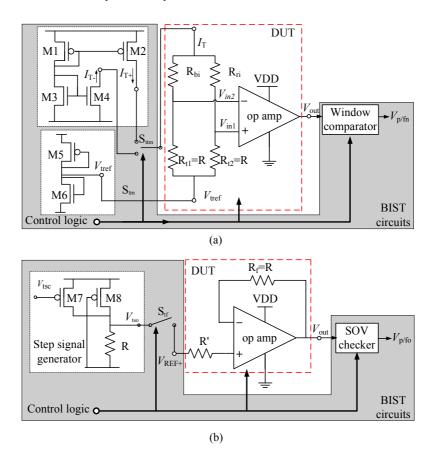

Figure 2.3(a) depicts the BIST system architecture of the proposed SOV checking based test scheme, and the proposed BIST circuit is composed of a step signal generator, a SOV checker and logic control signals. During the test, the Op Amp under test is converted into a voltage follower by setting  $V_{TM}$  to logic '1', and then positive or negative step signal, generated by a on-chip stimulus generator, is input to the voltage follower. After this, the SOV checker observes the transient response  $V_{tr}$ , checks the SOV and generates a digital test result  $V_{p/f}$ . If  $V_{p/f}$  is logic '0', the CUT is determined as a faulty circuit, otherwise a fault-free circuit. The whole testing process is controlled by  $V_{TM}$  and the *Control Signals*. In the multi-Op Amp system shown in Fig. 2.3(b), the control signal  $Op_s$  was added to choose Op Amp to be tested.

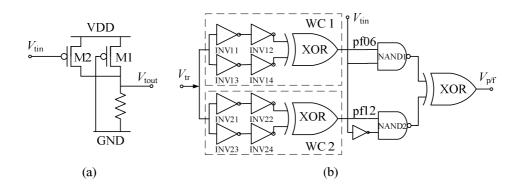

Figure 2.4(a) shows a step signal generator including two parallel pMOS transistors M1 of 3.4/0.4  $\mu$ m (W/L) and M2 of 2/0.4  $\mu$ m (W/L), and a resistor of 3.35k $\Omega$ . When input signal  $V_{\text{tin}}$  is set to logic '1', M2 is off, only M1 works, and the output  $V_{\text{tout}}$  is about 0.606V. On the other hand, when  $V_{\text{tin}}$  is set to logic '0', not only M1 but also M2 works, so the output  $V_{\text{tout}}$  changes to 1.202V. As a consequence, a step signal can be generated by switching the input of  $V_{\text{tin}}$ .

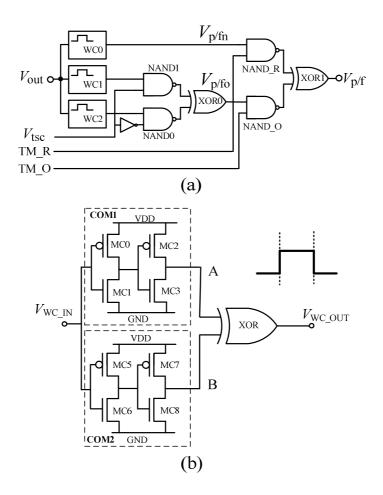

Figure 2.4(b) shows the circuit configuration of a SOV checker, which consists of two window comparators, two *NAND* gates and a *XOR* gate. Table 2.2 lists the aspect

ratio (W/L) settings of all transistors in the SOV checker.

**Figure 2.3** The proposed SOV checking based BIST architecture: (a) The single Op Amp case. (b) The multi-Op Amp case.

Figure 2.4 The BIST circuit configuration: (a) A step signal generator. (b) A SOV checker.

| Table 2.2 | Summary of element | s parameters in the SOV | checker shown | in Fig. 2.4(b). |

|-----------|--------------------|-------------------------|---------------|-----------------|

|-----------|--------------------|-------------------------|---------------|-----------------|

| Elements              | W/L (µm)  | Elements             | W/L (µm) |

|-----------------------|-----------|----------------------|----------|

| pMOS in INV11, INV12  | 0.6/0.4   | pMOS in INV21, INV22 | 36 /0.4  |

| nMOS in INV11,INV12   | 4 /0.4    | nMOS in INV21, INV22 | 0.6/0.4  |

| pMOS in INV13,INV14   | 0.6/0.4   | pMOS in INV23, INV24 | 33 /0.4  |

| nMOS in INV13, INV14  | 2.4/0.4   | nMOS in INV23, INV24 | 0.6/0.8  |

| Others in Fig. 2.4(b) | 0.54/0.18 |                      |          |

Owning to the process variation, the SOV cannot be exactly constant but fluctuates within a range according to the input step signal. Hence, the SOV checker checks the SOV in a range not a single value based on the Monte Carlo simulation results with transistor size variation of a maximum fluctuation of 5%.

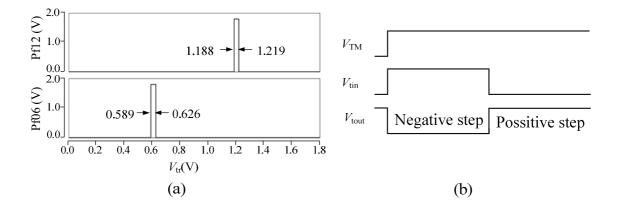

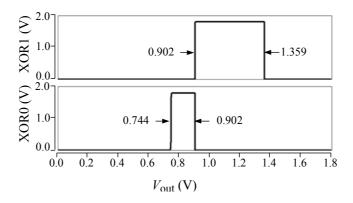

Under test mode, firstly the transient response  $V_{tr}$  shown in Fig. 2.4 (b) is simultaneously transmitted to two parallel window comparators of WC1 and WC2. As it can be seen from Fig. 2.5, If  $V_{tr}$  is in the checking region from 0.59V to 0.626V, WC1 outputs a logic high voltage, otherwise outputs a logical low voltage. In the same way, WC2's checking region is from 1.188V to 1.219V. In a word, when the  $V_{tr}$  is within the reference checking regions, the window comparator will output a logical high voltage.

**Figure 2.5** (a) The checking regions of *WC1* and *WC2*. (b) Control and data signals settings for test.

Then, the outputs of the two window comparators are separately transmitted to two *NAND* gates controlled by  $V_{\text{tin}}$ . When  $V_{\text{tin}}$  is logic '1', the output of *WC1* is valid and transmitted to the *XOR* gate to finally generate the test result  $V_{p/f}$  through *NAND1*, while the output of the *WC2* is blocked by *NAND2*. On the other hand, the output of *WC2* is valid and alternatively transmitted to the *XOR* gate.

As it was previously stated, the operation of the step signal generator and the SOV checker are controlled by  $V_{\text{TM}}$  and  $V_{\text{tin}}$ .  $V_{\text{TM}}$  converters the Op Amp under test into test mode and reconfigures it as a voltage follower, and then  $V_{\text{tin}}$  controls the step generator to form a step signal shown in Fig. 2.5(b) and the SOV checker to generate a valid test result  $V_{\text{p/f}}$ . Additionally, to simplify the test circuit, time delay element wasn't applied in this work to generate step signal, but a step generation controlling signal  $V_{\text{tin}}$  was added.

#### 2.2.3. Simulation Results

To evaluate the proposed SOV checking based BIST architecture, three Op Amps

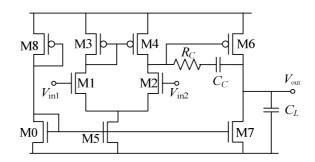

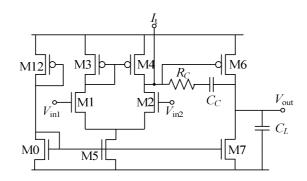

have been considered as test vehicles with different architectures. They are two-stage Op Amp, folded-cascode Op Amp and buffered Op Amp [75], and shown in Fig. 2.6, Fig. 2.7 and Fig. 2.8. The element sizes of the three Op Amps are listed in Table 2.3. In order to focus on the basic architecture of the Op Amps under test, the current biasing circuits were simplified to a pMOS transistor. In the case of complicated biasing circuit, the biasing circuit should be tested by the designed BIST circuits, even though the faulty biasing pMOS would reflect some faulty behaviors of other complicated biasing circuits.

Those three Op Amps with the proposed BIST system were laid out using Rohm CMOS 0.18-µm technology in Cadence environments and simulated by HSpice. As it is shown in Fig. 2.9, the proposed BIST circuit caused extra approximately 6.2% area overhead to the original three Op Amps.

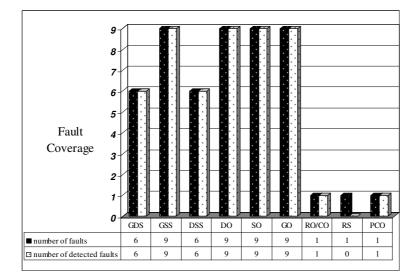

With reference to the listed catastrophic fault models for transistor, resistor and capacitor in Sect. 1.3, the faults were injected into the each Op Amp under test to evaluate the proposed BIST technique. In the case of two-stage Op Amp, 49 faults were detected in the total 52 faults, with fault coverage of approximately 94.2%. The undetected faults are the short faults in the compensation resistor  $R_{\rm C}$  and capacitor  $C_{\rm C}$ , and the GO in M8 shown in Fig. 2.6. Although the GO in the current biasing pMOS M8 changed the bias current that would degrade gain, it did not significantly change the SOV of the transient based on the voltage follower configuration of the two-stage Op Amp under test.

In the cases of the folded-cascode Op Amp, 80 faults of the total 93 injected faults were detected with the coverage of approximately 86%. In the cases of the buffered Op Amp, 131 faults were injected in the circuit, and 119 faults were finally detected with the fault coverage of approximately 91%. In the folded-cascode and buffered Op Amps, the main hard-detected faults exist in the cascode current mirrors, since they still can provide an almost constant current, even the faults happened. In addition, the GO of the current biasing pMOS and the faults in the compensation circuit were not detected by the checking the SOV of the transient response, since they change the Op Amp's characteristics in frequency domain.

Figure 2.6 The circuit configuration of the two-stage Op Amp.

Figure 2.7 The circuit configuration of the folded-cascode Op Amp.

Figure 2.8 The circuit configuration of the buffered Op Amp.

| Op Amp    | Elements        | Size (unit)      | Elements | Size (unit)       |

|-----------|-----------------|------------------|----------|-------------------|

|           | M0, M5          | 5.4/0.4 W/L(µm)  | M1, M2   | 12/0.4 W/L (µm)   |

| Two-stage | M3, M4          | 10.2/0.4 W/L(µm) | M6       | 34/0.4 W/L (µm)   |

| Op Amp    | M7              | 9/0.4 W/L(µm)    | M8       | 0.8/0.4 W/L (µm)  |

| Shown in  | $R_C$           | 18 kΩ            | $C_C$    | 0.8 pF            |

| Fig. 2.6  | $C_L$           | 10 pF            |          |                   |

| Cascode   | M0, M3          | 12/0.4 W/L(µm)   | M1, M2   | 39.8/0.4 W/L (µm) |

| Op Amp    | M4-M7, M13, M14 | 38.8/0.4 W/L(µm) | M8-M11   | 12.8/0.4 W/L (µm) |

| Shown in  | M12             | 10/0.4 W/L(µm)   | M15      | 4/0.4 W/L (μm)    |

| Fig. 2.7  | R0, R1          | 5 kΩ             | $C_L$    | 10 pF             |

|           | M0, M3          | 5.4/0.4 W/L(µm)  | M1, M2   | 32/0.4 W/L (µm)   |

| Buffered  | M4-M11, M17     | 36/0.4 W/L(µm)   | M12-M15  | 16.8/0.4 W/L (μm) |

| Op Amp    | M16             | 12/0.4 W/L(µm)   | M18, M21 | 40/0.4 W/L (µm)   |

| Shown in  | M19             | 5.6/0.4 W/L(µm)  | M20      | 14/0.4 W/L (µm)   |

| Fig. 2.8  | M22             | 4/0.4 W/L(µm)    | $C_C$    | 1.4 pF            |

|           | $C_L$           | 1 pF             |          |                   |

Table 2.3

Summary of elements parameters of the three Op Amps.

Figure 2.9 The layout pattern of the three Op Amps with the BIST circuits.

The comparisons of performances between the three original Op Amps and them with the BIST circuit shown from Table 2.4 to Table 2.6 indicate that the on-chip test circuits did not cause significant performance degradation, because the BIST circuit would be disconnected to the CUTs by turning off the analog switches.

**Table 2.4** Performance parameters of the original two-stage Op Amp and the two-stage Op Ampwith inclusion of the BIST circuit.

| Two-stage Op Amp                | Simulated Values   |                      |

|---------------------------------|--------------------|----------------------|

| Performances                    | Original Op Amp    | Op Amp with BIST     |

| Offset Voltage                  | -80 μV             | -80 μV               |

| DC Gain                         | 74.218 dB          | 74.205 dB            |

| Unity Gain Bandwidth            | 25.336 MHz         | 25.254 MHz           |

| Phase Margin                    | 66.34 Degree       | 65.154 Degree        |

| Slew Rate                       | +60.12/-4.83(V/µS) | +56.2/-4.9 (V/µS)    |

| Power Supply Rejection Ratio+/- | 96.94 dB /99.74 dB | 96.937 dB /99.746 dB |

Table 2.5Performance parameters of the original folded-cascode Op Amp and the folded-cascodeOp Amp with inclusion of the BIST circuit.

| Folded-cascode Op Amp           | Simulated Values   |                     |

|---------------------------------|--------------------|---------------------|

| Performances                    | Original Op Amp    | Op Amp with BIST    |

| Offset Voltage                  | -0.4 mV            | -0.4 mV             |

| DC Gain                         | 70.492 dB          | 70.492 dB           |

| Unity Gain Bandwidth            | 9.187 MHz          | 9.183 MHz           |

| Phase Margin                    | 87.667 Degree      | 86.617 Degree       |

| Slew Rate                       | +6.59/-7.77 (V/μS) | +6.22/-7.56 (V/μS)  |

| Power Supply Rejection Ratio+/- | 95.65 dB /96.49 dB | 96.646 dB /96.32 dB |

**Table 2.6** Performance parameters of the original buffered Op Amp and the buffered Op Amp withinclusion of the BIST circuit.

| Buffered Op Amp                 | Simulated Values     |                      |

|---------------------------------|----------------------|----------------------|

| Performances                    | Original Op Amp      | Op Amp with BIST     |

| Offset Voltage                  | 60 µV                | 60 µV                |

| DC Gain                         | 45.37 dB             | 45.374 dB            |

| Unity Gain Bandwidth            | 36.314 MHz           | 36.137 MHz           |

| Phase Margin                    | 74.8 Degree          | 71.247 Degree        |

| Slew Rate                       | +44.98/-42.58 (V/µS) | +44.37/-41.1 (V/μS)  |

| Power Supply Rejection Ratio+/- | 68.904 dB /76.586 dB | 68.904 dB /76.586 dB |

#### 2.2.4. Conclusions

This section has proposed a BIST scheme for Op Amp, and it can test all the Op Amps in the same chip, even these Op Amps are designed with different architectures. Throughout the test procedure, the possible faults can be detected by checking the SOV of transient response. Seen from the simulation results of the three test vehicles, the proposed test BIST system with fixed parameters setting can test the Op Amps with high fault coverage. Therefore, the proposed scheme can be an alternative and effective test approach for Op Amps in the same analog and mixed-signal system.

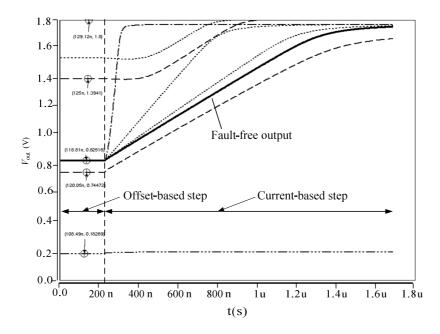

## 2.3. A Two-Step BIST Technique for Op Amp

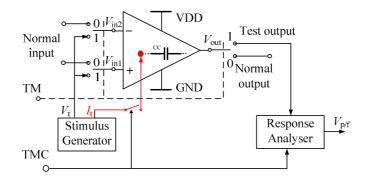

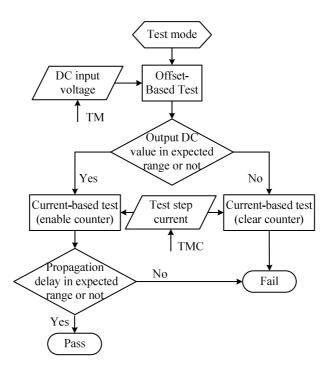

The transient response analysis based test techniques are the most feasible for BIST technique, but some slight performance parameters deviations are still hard to be captured because of the feedback network, that is to say the difference between faulty response and fault-free responses is too small to distinguish the faulty responses from the fault-free response by the on-chip test circuits. Thus, another feasible two-step BIST technique for Op Amp was proposed to improve the fault coverage, specifically for the compensation circuit. At the first offset-based test stage, a DC voltage is employed as test stimulus to the Op Amp configured as comparator. Then, at the second current-based test stage, a step current is injected to the compensation circuit to mainly excite the faults in the compensation circuit. In addition to the catastrophic faults, the proposed technique can particularly detect the capacitance variation in the compensation capacitor by combining the current-based test with the offset-based test. The circuit-level simulation results of the proposed BIST scheme are presented to demonstrate the feasibility of the proposed BIST scheme with high fault coverage of 98%.

#### 2.3.1. The Two-Step Test Strategy

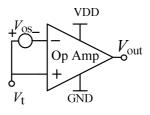

The input offset voltage of an Op Amps with differential inputs and single-ended output is defined as the differential input voltage for which the DC output voltage is midway between the supplies. The offset voltage of an Op Amp is composed of two components: the systematic offset and the random offset. The former results from the design of the circuit and is present even when all the matched devices in the circuit are identical, the latter results from mismatches in supposedly identical pairs of devices [77]. It can be seen from Fig. 2.10, an offset compensation voltage  $V_{os}$  must be added to compensate the output value to the approximate midway between the supplies due to the impact of the mismatches in the Op Amp; otherwise the DC value of  $V_{out}$  might be driven to the positive or negative power supply. In fact, in order to meet the acceptable offset voltage in some applications and also to make the transistors operate in saturation region, the DC output  $V_{out}$  should be located between power supplies even without the external offset compensation. Therefore, the offset-based test can be employed, the  $V_{out}$  is considered as test variable to monitor the mismatch changes caused by physical defects when the inputs of Op Amp are connected to a test reference voltage  $V_t$  at approximate midway between the supplies.

Figure 2.10 The offset compensation for an Op Amp.

At the offset-based test stage, some faults are still hard-detected, especially for the compensation circuit. These faults can be detected by checking the frequency-domain parameters like open loop gain, phase margin and unity-gain bandwidth, but on-chip test circuits for measuring frequency-domain parameters would be difficult to implement due the complexity, and also lead to unacceptable area overhead. Therefore, an alterative transforming test [75] is employed to measure the overshoot in transient response to reflect phase margin deviation. However, some faults just cause a slight slew rate and overshoot deviation in the transient response, and so some hard-detected faults of offset-based test are still hardly detected by the transient test, since the on-chip testing circuit is hard to observe this kind of slight deviation. For the purpose of increasing the deviation caused by the faults in the compensation circuit, a current-based test stage is employed to detect the hard-detected faults of the offset-based test stage.

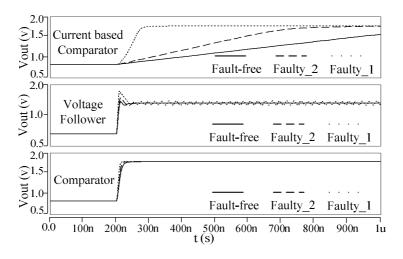

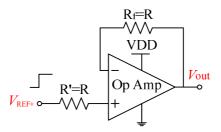

In the current-based test stage, the current is directly injected to compensation circuit, so the deviation caused by the possible faults in the compensation circuit can be utmost reflected on the output of the Op Amp under test. Figure 2.11 shows the

comparisons of the fault-free output response and the faulty responses. *Fault\_1* and *fault\_2* are short and 50% capacitance variation of the compensation capacitor, respectively. The Op Amp was simulated under current-based test based on the configurations of current-based comparator, voltage follower and comparator, respectively. The injected current in the current-based comparator configuration caused greatest differences between faulty responses and fault-free response, so the hard-detected faults can be easily detected through differentiating the faulty responses from the fault-free response. Consequently, in order to increase fault coverage the offset-based and current-based tests are combined to test the Op Amp.