# Hardware/software co-design for Neural Network trained by improved Particle Swarm Optimization

by

### DANG TUAN LINH

Student ID Number: 1188001

A dissertation submitted to the Engineering Course, Department of Engineering, Graduate School of Engineering, Kochi University of Technology, Kochi, Japan

in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Assessment Committee:

Supervisor: Yukinobu Hoshino Co-Supervisor: Masayoshi Tachibana Co-Supervisor: Yukio Mitsuyama Shinichi Yoshida Kiminori Matsuzaki

September 2017

### Abstract

Nowadays, using the particle swarm optimization (PSO) algorithms to train neural networks (NN) has become an attractive research. A famous method used to train the NNs is the back-propagation (BP) algorithm. Recently, previous studies have shown that the NN trained by PSO algorithms (NN-PSO) obtained higher recognition rates and lower learning errors when compared to the NN trained by the conventional BP algorithm. However, the standard PSO (SPSO) algorithm may stick to a local minimum in the training process. In this situation, the SPSO algorithm is stopped, leading to a high learning error rate or a low recognition rate of the trained NN. So far few studies have tried to overcome this problem by adding improving the standard PSO algorithms. Normally in previous studies, the improved versions of the PSO required to add more compute-intensive tasks that often increase computational burden the SPSO algorithm. Typically, previous researchers have implemented the NN trained by PSO algorithms only in hardware or only in software. Normally, the hardware implementation of the NN-PSO in these studies has been tested in a simulation using ModelSim program with the SPSO algorithm but it has not been tested in the real classification tasks. The FPGA-based NN was commonly investigated with a function-approximation, and the researchers just focused on reducing learning errors in the training phase.

To deal with the issues described above, this research has three objectives. The first objective is to introduce the improved particle swarm optimization (PSO) algorithms which overcome the premature convergence of the standard PSO (SPSO) algorithm without adding many computational tasks or compute-intensive functions to the SPSO algorithm.

The second objective is to propose co-design architectures between hardware and software for the NN-PSO. Compared to the hardware-only approach, the proposed co-design approach not only maintains the testing speed but also reduces the required FPGA resources concerning the logic elements and the memory bits previously reserved for the hardware implementation of the PSO algorithms. Compared to the software-only approach, the proposed co-design approach preserves the flexibility during in the training phase while obtaining the higher operating speed in the testing phase. The flexibility of the co-design is an easiness to modify the PSO parameters or change the PSO algorithms without redesigning or rebuilding the FPGA part.

The third objective is to investigate the performances concerning the learning errors and recognition rates in classification tasks of the NN trained by PSO algorithms implemented in a real FPGA device with the proposed co-design architectures comparing to the NN trained by the standard and dissipative PSO (SPSO, DPSO) presented in previous studies. The DPSO algorithm is chosen because it keeps the particles out of the local minimum without adding many tasks to the PSO algorithm.

Concerning the first objective, three different PSO algorithms which only change the velocity update function of the SPSO algorithm were proposed called the wPSOd\_CV, the PSOseed, and the PSOseed2 algorithm. The first PSO algorithm introduced in this chapter is the wPSOd\_CV algorithm that has two main components called the velocity control and the weight control. The velocity control has a jump phase to increase the velocity of the particle so that particle can move to another searching area to avoid the premature convergence. The weight control is used to balance between the exploitation task and the exploration task of the wPSOd\_CV algorithm. The wPSOd\_CV algorithm has some drawbacks. Even modifying only the velocity update function, this algorithm adds two operations, increasing the compute-intensive tasks of the SPSO algorithm. In addition, the jumping phase in the velocity control mechanism always has very big jumps. If the searching area has many solutions, the wPSOd\_CV has the possibility to meet other solutions and jump to other searching space before the before meeting the best solution. This issue leads to a possibility to ignore the best solution or require more iterations to reach the best solution. To overcome these drawbacks, the PSOseed algorithm is proposed. Avoiding jumping phases, for each particle the PSOseed algorithm uses a new variable called the seed position that is randomly generated in the initial phase of the algorithm. In each iteration, each particle is attracted and pulled to the position of its seed. The seed mechanism could reduce the possibility that the particle falls in a local minimum. Compared to the wPSOd\_CV algorithm, the PSOseed algorithm does not use any division operator and use fewer multiplication operators. A limitation is that the PSOseed algorithm highly depends on the generated seeds. The performance of the PSOseed significantly is reduced if the seeds are poorly generated. This thesis also introduces the PSOseed2 algorithm to solve the issue concerning the seed positions of the PSOseed algorithm by proposing a seed control mechanism. The operation of the PSOseed2 algorithm is similar to the PSOseed algorithm. However, in each iteration, all seed positions will be reseeded if the particles in the PSOseed2 algorithm cannot find a better position when the fitness value of the algorithm does not change.

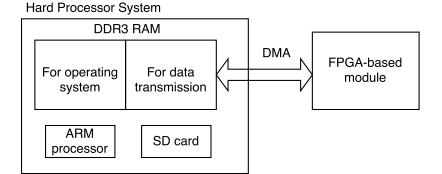

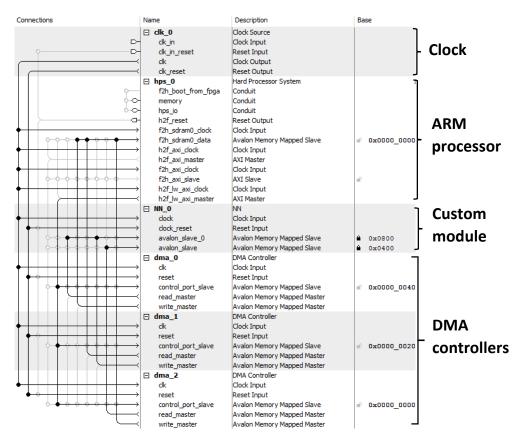

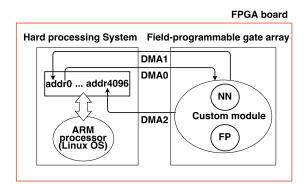

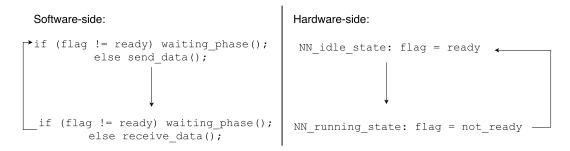

Regarding the second objective, the NN is implemented in hardware to maintain the testing speed of the hardware-based program while the PSO is implemented in software to keep the flexibility of the software-based program. Furthermore, the software implementation of the PSO algorithms can also reduce the FPGA resources previously reserved for the PSO algorithms. Three different co-design architectures were presented based on the proposed partitioning methodology. The first architecture uses the NIOS II processor. The second architecture replace the NIOS II by the ARM processor. This architecture has also other improvements such as the using of direct-memory access or

random-access memory. The third architecture combines the ARM approach in the second architecture with the FPGA-based PCA to reduce the required resources but still maintain the accuracy of the NN trained by PSO algorithms concerning the recognition rates and the learning errors. Experimental results confirmed both the speed advantage of the proposed co-design approach when compared with the software-only approach and the resource advantage of the proposed co-design approach when compared with the hardware-only approach. Results also showed that the hardware-based PCA can reduce the required resources of the program while keeping high recognition rates. In terms of the third objective, the NN was trained by three proposed PSO algorithms (wPSOd\_CV, PSOseed, PSOseed2) and two PSO algorithm presented in previous studies (SPSO, DPSO) in all three proposed co-design architectures. Experimental results demonstrated that the NN trained by the proposed algorithms, especially the PSOseed2 algorithm, had the highest performances concerning the recognition rates and the learning errors in all three architectures.

### Acknowledgements

First of all, I would like to thank Professor Yukinobu Hoshino for his willingness to coach me, his promptness, the eye-opening discussions we had and his valuable comments on the progress of my research. In the same light, I thank my co-Supervisors, Professor Masayoshi Tachibana and Professor Yukio Mitsuyama for their excellent observations, ideas, and creativity that inspired my dissertation. I would like to thank all the professors at the Kochi University of Technology who were responsible for the Ph.D. courses that I have attended during these years. I have acquired considerable knowledge through their presentations and interactive scientific discussions. I would like to present all my gratitude to Dr. Cao Thang at the University of Tokyo for his constructive advice and interesting ideas. Thank you also to Mr. Keita Mitani, Mr. Yuki Shinomya and other friends in Hoshino Laboratory at Kochi University of Technology for creating the best working conditions. I would also like to thank all Vietnamese friends of Kochi University of Technology for their friendship and support over the past three years. To all of them, I would like to express my sincere greetings. Additionally, I would like to thank all office staffs of International Relations Division, Kochi University of Technology. Finally, countless thanks and acknowledgements go to my family, especially, my wife and my daughter, for giving me their caring support and understanding.

# Contents

| Abstract         |                            |                                                                                                              |     | ii       |  |  |  |  |

|------------------|----------------------------|--------------------------------------------------------------------------------------------------------------|-----|----------|--|--|--|--|

| Acknowledgements |                            |                                                                                                              |     | vi       |  |  |  |  |

| Li               | st of                      | Figures                                                                                                      |     | xii      |  |  |  |  |

| Li               | st of                      | Tables                                                                                                       |     | xiv      |  |  |  |  |

| 1                | Intr                       | oduction                                                                                                     |     | <b>2</b> |  |  |  |  |

|                  | 1.1                        | Overview                                                                                                     |     | . 2      |  |  |  |  |

|                  | 1.2                        | Research objectives                                                                                          |     | . 4      |  |  |  |  |

|                  | 1.3                        | Structure of the dissertation                                                                                | • • | 5        |  |  |  |  |

|                  | Refe                       | rences                                                                                                       | • • | 6        |  |  |  |  |

| <b>2</b>         | Bac                        | ground                                                                                                       |     | 12       |  |  |  |  |

|                  | 2.1                        | Neural network                                                                                               |     | 12       |  |  |  |  |

|                  | 2.2                        | Particle swarm optimization algorithms in previous studies                                                   |     |          |  |  |  |  |

|                  |                            | 2.2.1 Standard particle swarm optimization algorithm                                                         |     |          |  |  |  |  |

|                  |                            | 2.2.2 Dissipative PSO algorithm                                                                              |     |          |  |  |  |  |

|                  | 2.3                        | NN trained by the PSO algorithms                                                                             |     |          |  |  |  |  |

|                  | Rete                       | ences                                                                                                        | • • | . 19     |  |  |  |  |

| 3                | Proposed PSO algorithms 20 |                                                                                                              |     |          |  |  |  |  |

|                  | 3.1                        | Introduction                                                                                                 |     | 20       |  |  |  |  |

|                  | 3.2                        | Proposed wPSOd_CV algorithm                                                                                  | •   | . 21     |  |  |  |  |

|                  |                            | 3.2.1 Introduction $\ldots$ |     |          |  |  |  |  |

|                  |                            | 3.2.1.1 Velocity control $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                    | •   | . 22     |  |  |  |  |

|                  |                            | $3.2.1.2  \text{Weight control}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $            | •   |          |  |  |  |  |

|                  |                            | 3.2.2 Discussion $\ldots$   |     |          |  |  |  |  |

|                  | 3.3                        | Proposed PSOseed algorithm                                                                                   |     |          |  |  |  |  |

|                  |                            | 3.3.1 Introduction                                                                                           |     |          |  |  |  |  |

|                  |                            | 3.3.2 Discussion                                                                                             |     |          |  |  |  |  |

|                  | 3.4                        | Proposed PSOseed2 algorithms                                                                                 | • • |          |  |  |  |  |

|                  |                            | 3.4.1 Introduction                                                                                           |     |          |  |  |  |  |

|                  | a -                        | 3.4.2 Discussion                                                                                             |     |          |  |  |  |  |

|                  | 3.5                        | Discussion                                                                                                   |     |          |  |  |  |  |

|                  | Refe                       | ences                                                                                                        |     | . 28     |  |  |  |  |

|   | Pro                       | -                                                                                                     | partitioning methodology for the NN-PSO                                                                                   | 30                                                                                                                        |

|---|---------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

|   | 4.1                       | Intro                                                                                                 | luction                                                                                                                   | . 30                                                                                                                      |

|   | 4.2                       | Prope                                                                                                 | sed partitioning methodology                                                                                              | . 31                                                                                                                      |

|   | 4.3                       | Opera                                                                                                 | ations on the software side $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$              | . 33                                                                                                                      |

|   | 4.4                       | Discu                                                                                                 | ssion $\ldots$                                                                                                            | . 35                                                                                                                      |

|   | Refe                      | erences                                                                                               |                                                                                                                           | . 35                                                                                                                      |

| 5 | Dno                       | noad                                                                                                  | co-design architecture using the NIOS II processor                                                                        | 38                                                                                                                        |

| 9 | <b>Frc</b><br>5.1         | -                                                                                                     | luction                                                                                                                   |                                                                                                                           |

|   | $5.1 \\ 5.2$              |                                                                                                       | psed architecture                                                                                                         |                                                                                                                           |

|   | 0.2                       | 5.2.1                                                                                                 | Overview                                                                                                                  |                                                                                                                           |

|   |                           | 5.2.1<br>5.2.2                                                                                        | The FPGA-based custom module                                                                                              |                                                                                                                           |

|   |                           | 5.2.2                                                                                                 | Connections between hardware and software                                                                                 |                                                                                                                           |

|   |                           | 0.2.0                                                                                                 | 5.2.3.1 Operation                                                                                                         |                                                                                                                           |

|   |                           |                                                                                                       | $5.2.3.2$ Implementation $\ldots$                                                                                         |                                                                                                                           |

|   | 5.3                       | Exper                                                                                                 | iments                                                                                                                    |                                                                                                                           |

|   | 0.0                       | 5.3.1                                                                                                 | Performances of he NN trained by PSO algorithms                                                                           |                                                                                                                           |

|   |                           | 0.0.1                                                                                                 | 5.3.1.1 Heart disease database                                                                                            |                                                                                                                           |

|   |                           |                                                                                                       | 5.3.1.2 Iris database                                                                                                     |                                                                                                                           |

|   |                           | 5.3.2                                                                                                 | Operations of the proposed co-design architecture using NIOS II                                                           | . 15                                                                                                                      |

|   |                           | 0.0.2                                                                                                 | processor                                                                                                                 | . 51                                                                                                                      |

|   |                           |                                                                                                       | 5.3.2.1 Operating Speed                                                                                                   |                                                                                                                           |

|   |                           |                                                                                                       | 5.3.2.2 Required resources                                                                                                |                                                                                                                           |

|   | 5.4                       | Discu                                                                                                 | ssion                                                                                                                     |                                                                                                                           |

|   |                           |                                                                                                       |                                                                                                                           |                                                                                                                           |

|   |                           |                                                                                                       |                                                                                                                           | -                                                                                                                         |

| 6 | Pro                       | -                                                                                                     | co-design architecture using the ARM processor                                                                            | 56                                                                                                                        |

|   | 6.1                       | Introc                                                                                                | 1                                                                                                                         | . 56                                                                                                                      |

|   | 6.2                       |                                                                                                       | luction                                                                                                                   |                                                                                                                           |

|   | 0.2                       | -                                                                                                     | sed architecture                                                                                                          | . 57                                                                                                                      |

|   | 0.2                       | Propo<br>6.2.1                                                                                        | sed architecture      Overview                                                                                            | .57                                                                                                                       |

|   |                           | 6.2.1<br>6.2.2                                                                                        | osed architecture                                                                                                         | .57<br>.57<br>.58                                                                                                         |

|   | 6.3                       | 6.2.1<br>6.2.2<br>Exper                                                                               | osed architecture          Overview          Connections between the software side and the hardware side          Siments | 57<br>57<br>57<br>58<br>61                                                                                                |

|   |                           | 6.2.1<br>6.2.2                                                                                        | osed architecture                                                                                                         | 57<br>57<br>58<br>61<br>62                                                                                                |

|   |                           | 6.2.1<br>6.2.2<br>Exper                                                                               | overview                                                                                                                  | . 57<br>. 57<br>. 58<br>. 61<br>. 62<br>. 63                                                                              |

|   |                           | 6.2.1<br>6.2.2<br>Exper                                                                               | overview                                                                                                                  | . 57<br>. 57<br>. 58<br>. 61<br>. 62<br>. 63<br>. 65                                                                      |

|   |                           | 6.2.1<br>6.2.2<br>Exper                                                                               | overview                                                                                                                  | . 57<br>. 57<br>. 58<br>. 61<br>. 62<br>. 63<br>. 65<br>. 67                                                              |

|   |                           | 6.2.1<br>6.2.2<br>Exper                                                                               | overview                                                                                                                  | . 57<br>. 57<br>. 58<br>. 61<br>. 62<br>. 63<br>. 65<br>. 67<br>. 69                                                      |

|   |                           | 6.2.1<br>6.2.2<br>Exper<br>6.3.1                                                                      | overview                                                                                                                  | . 57<br>. 57<br>. 58<br>. 61<br>. 62<br>. 63<br>. 65<br>. 67<br>. 69<br>. 69                                              |

|   |                           | 6.2.1<br>6.2.2<br>Exper<br>6.3.1<br>6.3.2                                                             | overview                                                                                                                  | . 57<br>. 57<br>. 58<br>. 61<br>. 62<br>. 63<br>. 65<br>. 65<br>. 67<br>. 69<br>. 69<br>. 71                              |

|   | 6.3<br>6.4                | <ul> <li>6.2.1</li> <li>6.2.2</li> <li>Exper</li> <li>6.3.1</li> <li>6.3.2</li> <li>Discur</li> </ul> | overview                                                                                                                  | . 57<br>. 57<br>. 58<br>. 61<br>. 62<br>. 63<br>. 65<br>. 65<br>. 67<br>. 69<br>. 71<br>. 73                              |

|   | 6.3<br>6.4                | <ul> <li>6.2.1</li> <li>6.2.2</li> <li>Exper</li> <li>6.3.1</li> <li>6.3.2</li> <li>Discur</li> </ul> | overview                                                                                                                  | . 57<br>. 57<br>. 58<br>. 61<br>. 62<br>. 63<br>. 65<br>. 65<br>. 67<br>. 69<br>. 71<br>. 73                              |

| 7 | 6.3<br>6.4<br>Refe        | 6.2.1<br>6.2.2<br>Exper<br>6.3.1<br>6.3.2<br>Discus                                                   | overview                                                                                                                  | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                      |

| 7 | 6.3<br>6.4<br>Refe        | 6.2.1<br>6.2.2<br>Exper<br>6.3.1<br>6.3.2<br>Discut<br>erences                                        | overview                                                                                                                  | . 57<br>. 57<br>. 58<br>. 61<br>. 62<br>. 63<br>. 65<br>. 65<br>. 67<br>. 69<br>. 69<br>. 71<br>. 73<br>. 74<br><b>76</b> |

| 7 | 6.3<br>6.4<br>Refe<br>7.1 | 6.2.1<br>6.2.2<br>Exper<br>6.3.1<br>6.3.2<br>Discusserences<br>posed<br>Introc                        | overview                                                                                                                  | . 57<br>. 57<br>. 58<br>. 61<br>. 62<br>. 63<br>. 65<br>. 67<br>. 69<br>. 71<br>. 73<br>. 74<br><b>76</b><br>. 76         |

| 7 | 6.3<br>6.4<br>Refe<br>Pro | 6.2.1<br>6.2.2<br>Exper<br>6.3.1<br>6.3.2<br>Discusserences<br><b>posed</b><br>Introc<br>Gener        | overview                                                                                                                  | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                      |

|              |      | 7.3.2   | Connections between FPGA side and software side 8                                                    | 0        |

|--------------|------|---------|------------------------------------------------------------------------------------------------------|----------|

|              |      | 7.3.3   | Operations of the NN-PCA                                                                             | 2        |

|              |      |         | 7.3.3.1 PCA training phase                                                                           | 2        |

|              |      |         | 7.3.3.2 NN training phase                                                                            | 3        |

|              | 7.4  | Experi  | iment                                                                                                | 4        |

|              |      | 7.4.1   | Performances of NN trained by the PSO algorithms 8                                                   | 5        |

|              |      |         | 7.4.1.1 Diabetic retinopathy debrecen dataset                                                        | 5        |

|              |      |         | 7.4.1.2 Wine dataset $\ldots \ldots $ | 7        |

|              |      | 7.4.2   | Operations of the NN-PCA architecture                                                                | 9        |

|              |      |         | 7.4.2.1 Required resources $\ldots \ldots \ldots \ldots \ldots \ldots \ldots $                       | 0        |

|              |      |         | 7.4.2.2 Operating speed $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 9$                  |          |

|              | 7.5  | Discus  | sion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $.$ 9                                     | 4        |

|              | Refe | erences |                                                                                                      | 4        |

| 8            | Con  | nclusio | n 9                                                                                                  | 6        |

| $\mathbf{A}$ | Soft | ware-c  | only architecture 10                                                                                 | 0        |

| в            | Har  | dware-  | -only architecture 10                                                                                | <b>2</b> |

# List of Figures

| 2.1  | Operation of one node in the NN                                                                 | 13 |

|------|-------------------------------------------------------------------------------------------------|----|

| 2.2  | Architecture of the NN                                                                          | 13 |

| 2.3  | Weights and biases of the NN                                                                    | 14 |

| 2.4  | Encoding vectors for one PSO particle in two different types of NN                              | 17 |

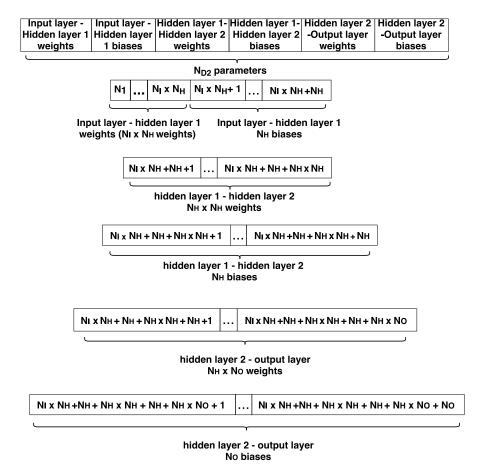

| 2.5  | Details of the encoding vectors for two-hidden-layer NN                                         | 18 |

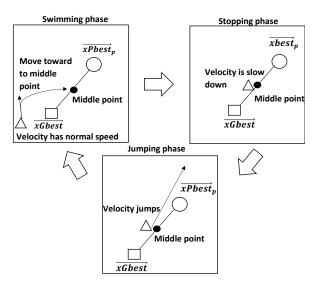

| 3.1  | Mechanism of the velocity control                                                               | 22 |

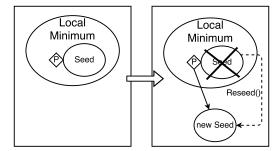

| 3.2  | Operation of the PSOseed2 algorithm                                                             | 27 |

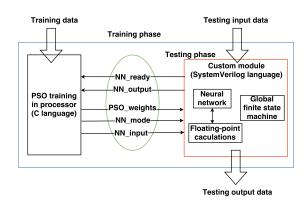

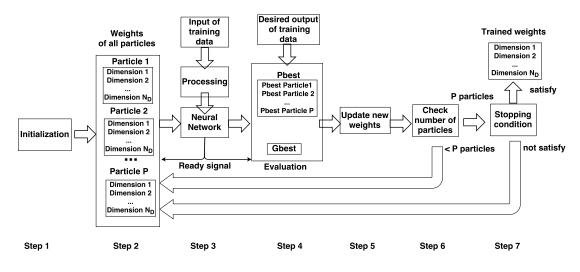

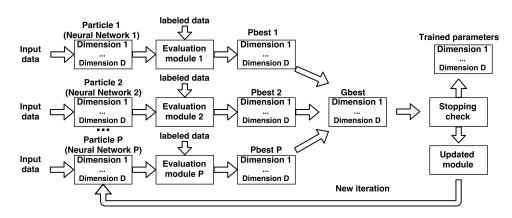

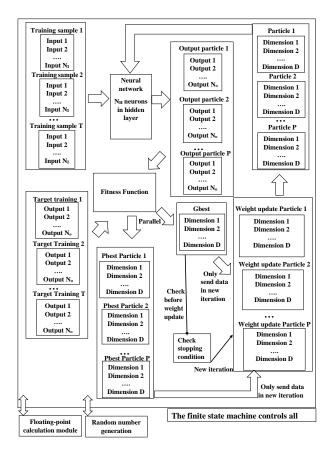

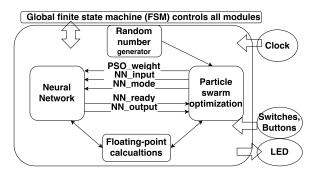

| 4.1  | Proposed partitioning methodology                                                               | 32 |

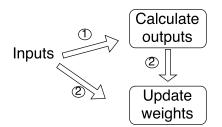

| 4.2  | Operations on the software side                                                                 | 33 |

| 5.1  | Proposed co-design with NIOS II processor                                                       | 40 |

| 5.2  | FSM of the FPGA-based component                                                                 | 41 |

| 5.3  | Synchronization between NN and floating-point submodule                                         | 41 |

| 5.4  | The FPGA-based component                                                                        | 43 |

| 5.5  | Avalon MM interface                                                                             | 44 |

| 5.6  | Custom module                                                                                   | 44 |

| 5.7  | Connections in NIOS II approach                                                                 | 45 |

| 5.8  | DE1-SoC board                                                                                   | 45 |

| 5.9  | NIOS II console                                                                                 | 46 |

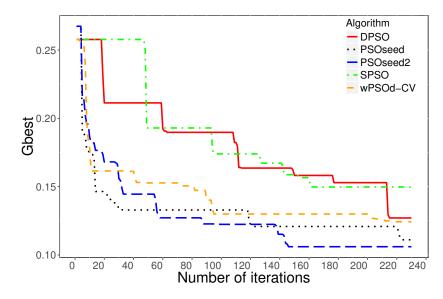

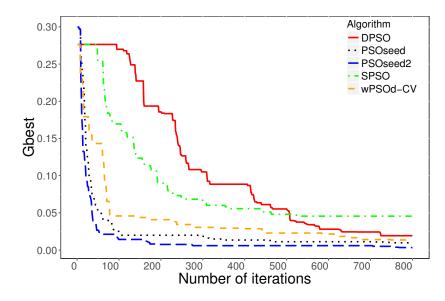

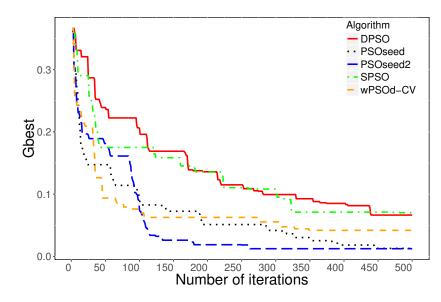

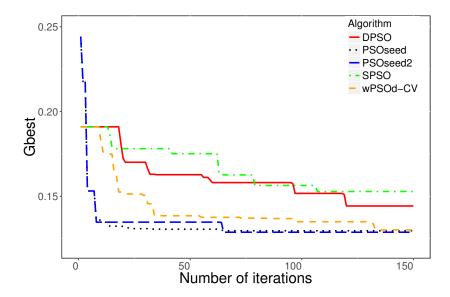

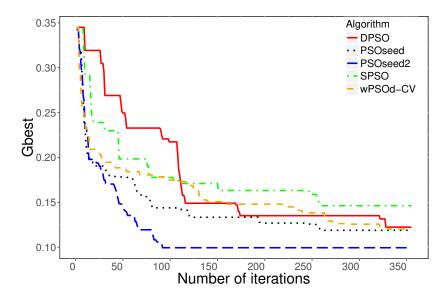

| 5.10 | Reduction of $Gbest$ with heart disease dataset, 100 training samples, 80                       |    |

|      | testing samples                                                                                 | 48 |

|      | Results with heart disease dataset, $80\ {\rm training\ samples},\ 100\ {\rm testing\ samples}$ | 48 |

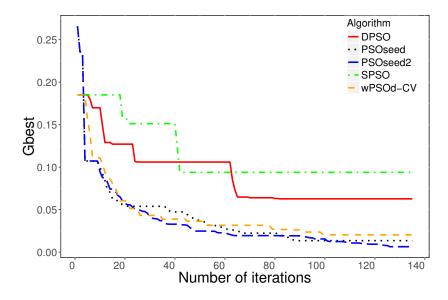

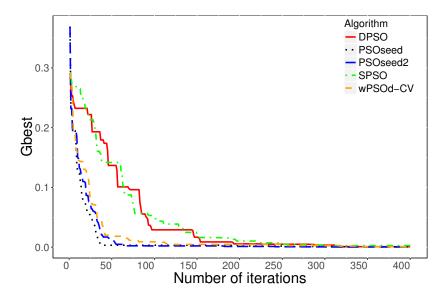

| 5.12 | Reduction of $Gbest$ with iris dataset, 45 training samples, 105 testing                        |    |

|      | samples                                                                                         | 50 |

| 5.13 | Reduction of $Gbest$ with Iris dataset 105 training samples, 45 testing                         |    |

|      | samples                                                                                         | 50 |

| 6.1  | ARM apporach for the NN trained by PSO algorithms                                               | 58 |

| 6.2  | Whole system in ARM approach                                                                    | 59 |

| 6.3  | Using of Direct Memory Acces (DMA)                                                              | 60 |

| 6.4  | The data transmission section                                                                   | 60 |

| 6.5  | Timing control by using $flag$                                                                  | 61 |

| 6.6  | Putty software                                                                                  | 62 |

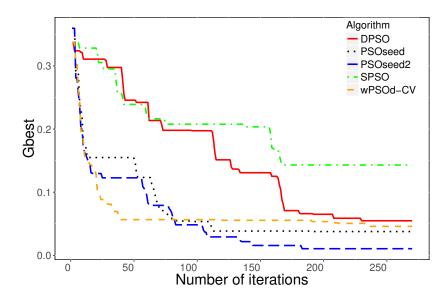

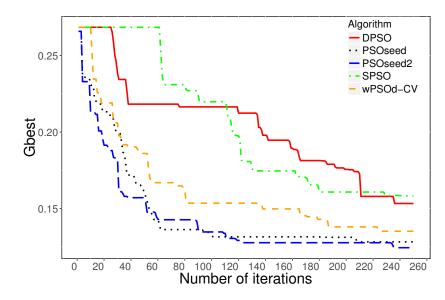

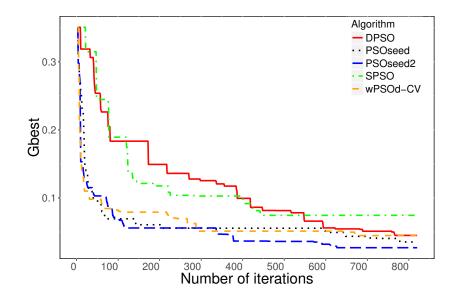

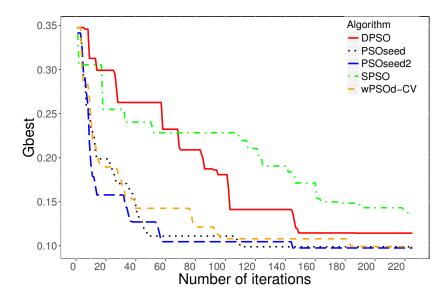

| 6.7  | Reduction of <i>Gbest</i> with wine dataset, 120 training samples, 58 testing samples           | 63 |

| 6.8  | Reduction of <i>Gbest</i> with Wine dataset with 58 training samples, 120                       | 00 |

| 0.0  | testing samples                                                                                 | 64 |

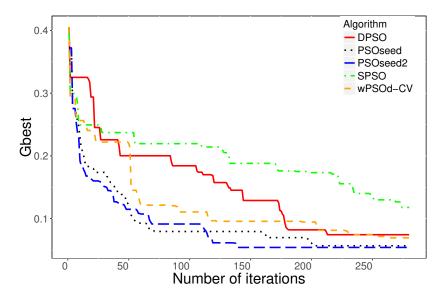

| 6.9  | Reduction of <i>Gbest</i> with Australian credit dataset, 490 training samples, 200 testing samples             | 66  |

|------|-----------------------------------------------------------------------------------------------------------------|-----|

| 6.10 | Reduction of <i>Gbest</i> with Australian credit dataset, 200 training samples, 490 testing samples             | 67  |

| 6.11 | Results with Iris dataset, 45 training samples, 105 testing samples                                             | 68  |

|      | Results with iris dataset 105 training samples, 45 testing samples                                              | 69  |

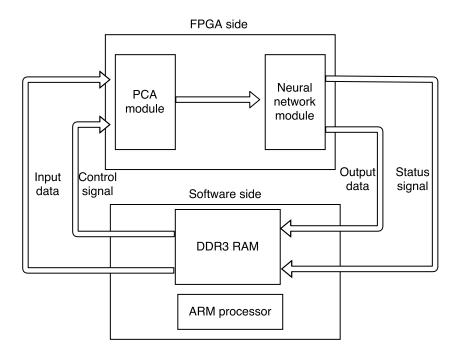

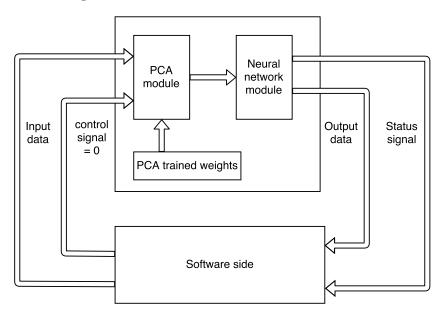

| 7.1  | Proposed NN-PCA architecture                                                                                    | 79  |

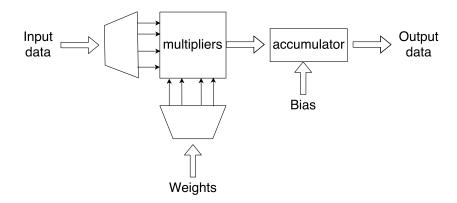

| 7.2  | Operation of one node in the NN                                                                                 | 80  |

| 7.3  | Connection with ALU module                                                                                      | 81  |

| 7.4  | Connections between hardware side and software side                                                             | 81  |

| 7.5  | PCA training task                                                                                               | 82  |

| 7.6  | Operation of the PCA module                                                                                     | 83  |

| 7.7  | NN training task                                                                                                | 83  |

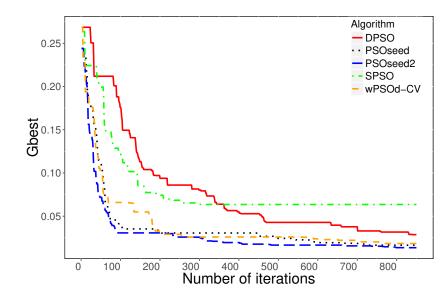

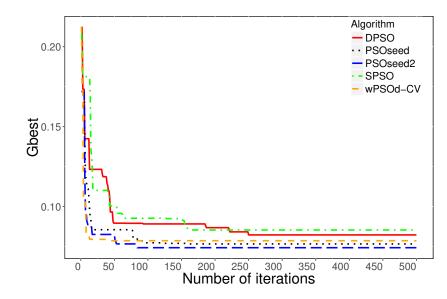

| 7.8  | Reduction of <i>Gbest</i> with diabetic retinopathy debrecen dataset, 450 training samples, 300 testing samples | 86  |

| 7.9  | Reduction of <i>Gbest</i> with diabetic retinopathy debrecen dataset, 300 training samples, 450 testing samples | 87  |

| 7.10 | Reduction of <i>Gbest</i> with wine dataset, 88 training samples, 90 testing samples                            | 88  |

| 7.11 | Reduction of <i>Gbest</i> with wine dataset 90 training samples, 88 testing samples                             | 89  |

| A.1  | The software-only architecture                                                                                  | 100 |

| B.1  | Algorithm of hardware implementation of training step                                                           | 102 |

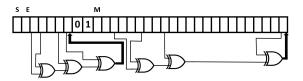

| B.2  | Initial value LFSR: s-sign bit, e-exponent bit, and m-mantissa bit                                              |     |

| B.3  | The hardware-only architecture                                                                                  |     |

# List of Tables

| 5.1  | List of experiments conducted with NIOS II approach                                  | 46 |

|------|--------------------------------------------------------------------------------------|----|

| 5.2  | Results with heart disease dataset, 100 training samples, 80 testing samples         | 47 |

| 5.3  | Results with heart disease dataset, 80 training samples, 100 testing samples         | 49 |

| 5.4  | Results of FPGA-based NN with iris dataset, 45 training samples                      | 50 |

| 5.5  | Results of Iris dataset, 105 training samples, 45 testing samples                    | 51 |

| 5.6  | The testing time in second                                                           | 52 |

| 5.7  | The logic utilization                                                                | 53 |

| 6.1  | List of experiments conducted with ARM approach                                      | 63 |

| 6.2  | Results of FPGA-based NN with wine dataset, 120 training samples, 58 testing samples | 64 |

| 6.3  | Results with wine dataset, 58 training samples, 120 testing samples                  | 65 |

| 6.4  | Results with Australian credit dataset, 490 training samples, 200 testing            |    |

| 6.5  | samples                                                                              | 65 |

| 0.0  | samples                                                                              | 66 |

| 6.6  | Results with Iris dataset, 45 training samples, 105 testing samples                  | 68 |

| 6.7  | Results of FPGA-based NN with iris dataset, 45 training samples, 105                 | 00 |

|      | testing samples                                                                      | 68 |

| 6.8  | The testing time in second by using DE1-SoC                                          | 71 |

| 6.9  | The testing time in second by using Intel processor                                  | 71 |

| 6.10 | Resources Utilization in percentage                                                  | 73 |

| 7.1  | List of experiments conducted with NN-PCA approach                                   | 85 |

| 7.2  | Results of FPGA-based NN with diabetic retinopathy debrecen dataset,                 |    |

| 7.3  | 450 training samples, 300 training samples                                           | 86 |

| 1.0  | 450 testing samples                                                                  | 87 |

| 7.4  | Results with wine dataset, 88 training samples, 90 testing samples                   | 88 |

| 7.5  | Results wine dataset, 90 training samples, 88 training                               | 89 |

| 7.6  | Results with diabetic retinopathy debrecen                                           | 90 |

| 7.7  | Results with wine dataset, 5 particles, 300 iterations, 5500 PCA                     | 91 |

| 7.8  | Results with wine dataset, 15 particles, 500 iterations, 5500 PCA                    | 92 |

| 7.9  | The testing time with diabetic retinopathy debrecen dataset, 350 testing             |    |

|      | samples in second                                                                    | 93 |

| 7.10 | The testing time with wine dataset, 90 training samples, 88 testing sam-             |    |

|      | ples in second                                                                       | 94 |

### Chapter 1

### Introduction

#### 1.1 Overview

A neural network (NN) has emerged as an attractive target for research. Several companies have also used the NN in the practical applications [1, 2]. The NN is invented for representing a human brain concerning two aspects. The first aspect relates to a knowledge acquisition. Both the NN and the human brain have a learning phase to acquire the knowledge from an environment. The second aspect is the knowledge presentation. The acquired knowledge after the training phase is stored in the form of the weights and biases of each node of both the NN and the human brain [3, 4].

Before the testing phase, the NN needs to be trained. During the training phase, the NN tried to find a set of parameters concerning the weights and biases which minimize the learning error. A famous method used in the training of the NN is the back-propagation (BP) algorithm. However, in previous studies have mentioned that the NN trained by the particle swarm optimization (PSO) algorithm had obtained higher recognition rates and lower learning errors when compared with the NN trained by the BP algorithm [5–7]. The PSO algorithm was introduced to simulate the social behavior such as a bird flocking or a fish schooling. At any given time, the movement of each particle in the swarm, for example, a bird or a fish, is always based on the knowledge of the best personal position of this particle and the best global position of the swarm. The best global position is evaluated from the best personal position of all particles [8–10].

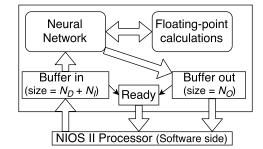

In the training phase of the NN using PSO algorithm, the position of each particle is an encoding vector that consists of all weights and biases of the NN. Each vector is a potential solution for the weights and biases of the NN. In this situation, if the NN has  $N_D$  weights and biases, the PSO particle is the  $N_D$ -dimensional vector. If the PSO training uses P particles, P encoding vectors will be employed. During the training phase, the movements of these P vectors are based on the PSO algorithm. In each position of the encoding vector, the learning error of the NN will be calculated using a fitness function. The goal of the PSO training is to find a position of the encoding vector which has the minimization of the learning error [5, 11].

In previous studies, the software implementation of the NN trained by PSO algorithm (NN-PSO) is already investigated [5, 11]. Several practical problems have been solved using the software-based NN-PSO [7, 12–15].

However, the standard PSO (SPSO) algorithm may stick to a local minimum during the training of the NN, and the training phase will be stopped. In this case, the NN cannot be trained. Thus, its learning error will be high, and its recognition rate will be low. To overcome this premature convergence of the SPSO algorithm, several different approaches have been introduced. The attractive and repulsive PSO (ARPSO) adds the repulsive phase. The diversity of the swarm calculated in each iteration of the swarm to determine whether the ARPSO operates in the attractive phase (the SPSO algorithm) or the repulsive phase [16]. The PSO with spatial particle extension (SEPSO) that adds the radius r to detect the collisions of all particles in the swarm. If the collisions occur, the particles will be bounced backward to prevent the situation when all particles stick to the local minimum [17]. The opposition-based PSO calculates the opposite particle of each particle in each iteration. If the opposite particle has a better fitness value than the original particle, this opposite particle will replace the original particle [18]. Other researchers use the multi-swarm strategy [19] or use not only the information of a particle but also the information of its neighborhood to calculate the new position of this particle [20]. Other solutions are to use the mutation operations such as the Cauchy mutation [21, 22], the Gaussian mutation [23, 24], or to combine the SPSO algorithm with the genetic algorithm [25]. The improved versions of the PSO in previous studies normally add more functions, more compute-intensive tasks to the SPSO algorithm. It is beneficial to investigate an improved version of the PSO algorithm to keep the particle out of the local minimum which does not add many functions or tasks to the SPSO algorithm.

Currently, a field-programmable gate array (FPGA) has also attracted many researchers. Compared with the software-based program, the FPGA-based program could obtain a higher operating speed because of the parallelism [26–28]. Compared with the graphics processing unit (GPU)-based program, the FPGA-based program has a lower power consumption [28–30]. In addition, the FPGA-based program is also portable because it can be implemented in a single FPGA chip and can operate without the need of having a processor. Several studies related hardware implementation of the NN [31], the SPSO [27], or even the NN-PSO have been published [32–34].

However, the hardware implementation of the NN-PSO was only tested in a simulation using ModelSim program, with the SPSO algorithm, or was not tested in the classification tasks. In these studies, the FPGA-based NN normally was used to investigate the function approximation, or the researchers only focus on the training phase of the NN-PSO by showing only the reduction of the learning errors [32–34]. It needs to investigate the hardware implementation of the NN-PSO in classification jobs using a real FPGA device.

In addition, the previous papers normally focus only on the hardware-only architecture [32–34]. In this situation, all components of the program were implemented in hardware. This approach required many FPGA resources regarding the logic elements and the memory bits. On the other hand, the FPGA device has the resource constraints because the FPGA resources are very expensive [35]. In addition, the hardware-only program is not flexible as the software-based program. It needs to rebuild and recompile the program each time we change the parameters [36]. Therefore, it is necessary to have a co-design architecture which can keep both the speed advantage of the FPGA-based program and the flexibility of the software-based program. This approach can also reduce the required FPGA resources previously reserved for the components which are already moved to the software-side.

### 1.2 Research objectives

To deal with the issues described above, this research has three main objectives. The first objective is to introduce the improved PSO algorithms which overcome the premature convergence of the SPSO algorithm without adding many computational tasks or compute-intensive functions to the SPSO algorithm.

The second objective is to propose co-design architectures between hardware and software for the NN-PSO. Compared to the hardware-only approach, the proposed co-design approach not only maintains the testing speed but also reduces the required FPGA resources concerning the logic elements and the memory bits previously reserved for the hardware implementation of the PSO algorithms. Compared to the software-only approach, the proposed co-design approach preserves the flexibility during the training phase while obtaining the higher operating speed in the testing phase. The flexibility of the co-design is an easiness to modify the PSO parameters or change the PSO algorithms without redesigning or rebuilding the FPGA part.

The third objective is to investigate the performances concerning the learning errors and recognition rates in classification tasks of the NN trained by PSO algorithms implemented in a real FPGA device with the proposed co-design architectures comparing to the NN trained by the standard and the dissipative PSO [37] (SPSO, DPSO) presented in previous studies. The DPSO algorithm is chosen because it keeps the particles out of the local minimum without adding many tasks to the PSO algorithm.

#### **1.3** Structure of the dissertation

This dissertation is divided into eight chapters, each of which deals with different accounts. The content of the dissertation is as follows.

- Chapter 1 briefly presents the overview and objectives of this research.

- Chapter 2 presents related work concerning the NN, the SPSO algorithm, and the DPSO algorithm. It also details how the NN can be trained using the PSO algorithms.

- Chapter 3 focuses on the premature convergence issue of the SPSO algorithm by proposing three improved versions of the SPSO algorithm called wPSOd\_CV, PSOseed, and PSOseed2.

- Chapter 4 describes the proposed partitioning methodology between hardware and software for the NN-PSO. The operations on the software side of the proposed partitioning methodology are also presented in this chapter.

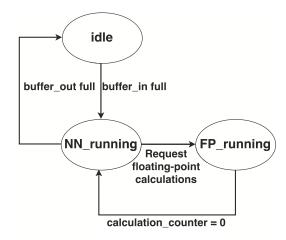

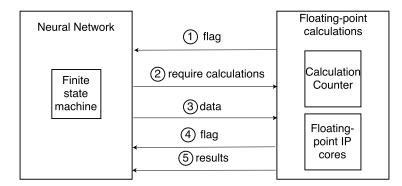

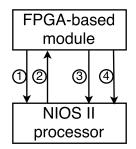

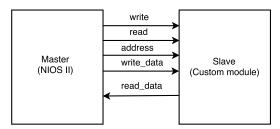

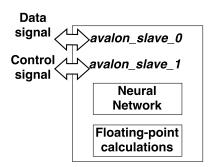

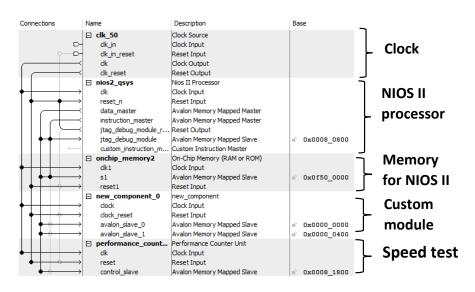

- Chapter 5 focuses on the first co-design architecture based on the partitioning methodology presented in chapter 4 which uses the NIOS II processor. This chapter also discusses the performances of the NN trained by proposed PSO algorithms in this architecture.

- Chapter 6 deals with the performances of the NN trained by proposed PSO algorithms in the second co-design architecture that uses the ARM processor. The

second co-design architecture is introduced to overcome the drawbacks of the first architecture using the NIOS II processor presented in chapter 5.

- Chapter 7 presents a method to improve performances of the NN trained by proposed PSO algorithms in the proposed co-design architectures. To reduce the required resources while maintaining the high recognition rate, this chapter proposes the third co-design architecture which is a combination between the co-design architecture using ARM processor introduced in chapter 6 and the FPGA-based principal component analysis. The performances of the NN trained by the proposed PSO algorithm in the third co-design architecture are also discussed in this chapter.

- Chapter 8 concludes all chapters and discusses the future directions for continuing the research.

### References

- Google uses neural networks to translate without transcribing new scientist. https://www.newscientist.com. (Accessed on 06/05/2017).

- [2] Swiftkey debuts world's first smartphone keyboard powered by neural networks swiftkey blog. https://blog.swiftkey.com. (Accessed on 06/05/2017).

- [3] S. Haykin. Neural networks and learning machines. Pearson Education, Upper Saddle River, NJ, third edition, 2009.

- [4] S. Haykin. Neural Networks: A Comprehensive Foundation. Prentice Hall, Upper Saddle River, NJ, USA, 2nd edition, 1998.

- [5] V. G. Gudise and G. K. Venayagamoorthy. Comparison of particle swarm optimization and backpropagation as training algorithms for neural networks. In *Proceedings* of the 2003 IEEE Swarm Intelligence Symposium, pages 110–117, Apr 2003.

- [6] I. Vilovic, N. Burum, and D. Milic. Using particle swarm optimization in training neural network for indoor field strength prediction. In 2009 International Symposium ELMAR, pages 275–278, Sep 2009.

- Z. A. Bashir and M. E. El-Hawary. Applying wavelets to short-term load forecasting using pso-based neural networks. *IEEE Transactions on Power Systems*, 24(1):20– 27, Feb 2009.

- [8] J. Kennedy and R. Eberhart. Particle swarm optimization. In Proceedings of the IEEE International Conference on Neural Networks, volume 4, pages 1942–1948, Nov 1995.

- [9] R. Poli, J. Kennedy, and T. Blackwell. Particle swarm optimization. Swarm Intelligence, 1(1):33–57, 2007.

- [10] R. Eberhart and J. Kennedy. A new optimizer using particle swarm theory. In Proceedings of the Sixth International Symposium on Micro Machine and Human Science, pages 39–43, Oct 1995.

- [11] R. Mendes, P. Cortez, M. Rocha, and J. Neves. Particle swarms for feedforward neural network training. In *Proceedings of the 2002 International Joint Conference* on Neural Networks, volume 2, pages 1895–1899, 2002.

- [12] N. Yançin, G. Tezel, and C. Karakuzu. Epilepsy diagnosis using artificial neural network learned by pso. Turkish Journal of Electrical Engineering & Computer Sciences, 23:421–432, 2015.

- [13] P. Khoury and D. Gorse. Investing in emerging markets using neural networks and particle swarm optimisation. In *Proceedings of the 2015 International Joint Conference on Neural Networks*, pages 1–7, July 2015.

- [14] K.W. Chau. Application of a pso-based neural network in analysis of outcomes of construction claims. Automation in Construction, 16(5):642–646, 2007. ISSN 0926-5805.

- [15] W. Z. Lu, H. Y. Fan, A. Y. T. Leung, and J. C. K. Wong. Analysis of pollutant levels in central hong kong applying neural network method with particle swarm optimization. *Environmental Monitoring and Assessment*, 79(3):217–230, 2002.

- [16] J. Riget and J.S. Vesterstrm. A diversity-guided particle swarm optimizer the arpso. Technical report, 2002.

- [17] T. Krink, J. S. Vesterstrom, and J. Riget. Particle swarm optimisation with spatial particle extension. In *Proceedings of the 2002 Congress on Evolutionary Computation*, volume 2, pages 1474–1479, 2002.

- [18] H. Wang, H. Li, Y. Liu, C. Li, and S. Zeng. Opposition-based particle swarm algorithm with cauchy mutation. In *Proceedings of the 2007 IEEE Congress on Evolutionary Computation*, pages 4750–4756, Sep 2007.

- [19] J. Jie, J. Zeng, C. Han, and Q. Wang. Knowledge-based cooperative particle swarm optimization. Applied Mathematics and Computation, 205(2):861 – 873, 2008.

- [20] R. Mendes, J. Kennedy, and J. Neves. The fully informed particle swarm: simpler, maybe better. *IEEE Transactions on Evolutionary Computation*, 8(3):204–210, Jun 2004.

- [21] H. Wang, C. Li, Y. Liu, and S. Zeng. A hybrid particle swarm algorithm with cauchy mutation. In *Proceedings of the 2007 IEEE Swarm Intelligence Symposium*, pages 356–360, Apr 2007.

- [22] A. Stacey, M. Jancic, and I. Grundy. Particle swarm optimization with mutation. In Proceedings of the 2003 Congress on Evolutionary Computation, volume 2, pages 1425–1430, Dec 2003.

- [23] N. Higashi and H. Iba. Particle swarm optimization with gaussian mutation. In Proceedings of the 2003 IEEE Swarm Intelligence Symposium, pages 72–79, Apr 2003.

- [24] Q. Wu. Power load forecasts based on hybrid pso with gaussian and adaptive mutation and wv-svm. Expert Systems with Applications, 37(1):194 – 201, 2010. ISSN 0957-4174.

- [25] B. Yang, Y. Chen, and Z. Zhao. A hybrid evolutionary algorithm by combination of pso and ga for unconstrained and constrained optimization problems. In *Proceedings* of the 2007 IEEE International Conference on Control and Automation, pages 166– 170, May 2007.

- [26] E. Monmasson and M. N. Cirstea. Fpga design methodology for industrial control systems - a review. *IEEE Transactions on Industrial Electronics*, 54(4):1824–1842, Aug 2007.

- [27] Y. Maeda and N. Matsushita. Simultaneous perturbation particle swarm optimization using fpga. In Proceedings of the 2007 International Joint Conference on Neural Networks, pages 2695–2700, Aug 2007.

- [28] J. A. G. Pulido, M. A. V. Rodriguez, J. M. S. Perez, S. P. Mendes, and V. Carreira. Accelerating floating-point fitness functions in evolutionary algorithms: a fpga-cpugpu performance comparison. *Genetic Programming and Evolvable Machines*, 12 (4):403–427, 2011.

- [29] D. Zou, Y. Dou, and F. Xia. Optimization schemes and performance evaluation of smithwaterman algorithm on cpu, gpu and fpga. Concurrency and Computation: Practice and Experience, 24(14):1625–1644, 2012.

- [30] K. Benkrid, A. Akoglu, C. Ling, Y. Song, Y. Liu, and X. Tian. High performance biological pairwise sequence alignment: FPGA versus GPU versus cell BE versus GPP. International Journal of Reconfigurable Computing, 2012, 2012.

- [31] S. Himavathi, D. Anitha, and A. Muthuramalingam. Feedforward neural network implementation in fpga using layer multiplexing for effective resource utilization. *IEEE Transactions on Neural Networks*, 18(3):880–888, May 2007.

- [32] Mehmet Ali Cavuslu, Cihan Karakuzu, and Fuat Karakaya. Neural identification of dynamic systems on fpga with improved pso learning. *Applied Soft Computing*, 12(9):2707 – 2718, 2012.

- [33] A. Bezborah. A hardware architecture for training of artificial neural networks using particle swarm optimization. In Proceedings of the 2012 Third International Conference on Intelligent Systems Modelling and Simulation, pages 67–70, Feb 2012.

- [34] C. J. Lin and H. M. Tsai. Fpga implementation of a wavelet neural network with particle swarm optimization learning. *Mathematical and Computer Modelling*, 47 (910):982 – 996, 2008.

- [35] D. G. Bailey. Design for Embedded Image Processing on FPGAs. Wiley Publishing, 1st edition, 2011.

- [36] S. A. Li, C. C. Hsu, C. C. Wong, and C. J. Yu. Hardware/software co-design for particle swarm optimization algorithm. *Information Sciences*, 181(20):4582–4596, 2011.

[37] X. F. Xie, W. J. Zhang, and Z. L. Yang. Dissipative particle swarm optimization. In Proceedings of the 2002 Congress on Evolutionary Computation, volume 2, pages 1456–1461, 2002.

### Chapter 2

### Background

Chapter 2 presents related work concerning the operation of the NN, the SPSO, and the DPSO algorithms. It also details how the NN can be trained using the PSO algorithms.

#### 2.1 Neural network

In previous studies, an artificial NN was proposed to represent a human brain. Similar to the operation of the human brain, the NN acquires the knowledge from the environment during the training phase. This collected knowledge is stored in the form of the weights and biases of each node in the NN. In each iteration of the training phase, each node in the NN tries to obtain a set of weights and biases which minimizes the learning error of the NN.

The resources of the hardware-based program concerning the logic elements and the memory bits are very expensive. On the other hand, the loops and the cycles in the hardware implementation require many resources of the FPGA device. To reduce the required resources of the FPGA-based program, this research focuses only on the feed-forward NN because the data in the feedforward NN only move in one direction without loops or cycles [1, 2].

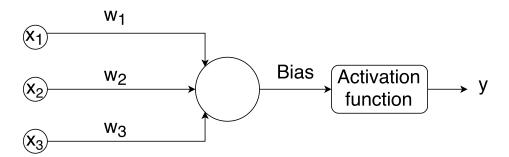

Typically, the feedforward NN has three different types of layers called the input layer, the hidden layer, and the output layer, respectively. The NN has only one input layer and one output layer, but it may have more than one hidden layers. Each layer consists of several nodes that connect to other nodes in the next and previous layers. The inputs of a node in one layer are multiplied by the weights in this layer. Then, this result becomes the input of nodes in the next layer through an activation function [1, 2]. The operation of one node in the NN is illustrated in Fig. 2.1. The calculated results x before the activation function is expressed in Eq. (2.1). This study uses the Sigmoid function as the activation function. Therefore, the output y is calculated according to Eq. (2.2). This output y is used as the input of the nodes in the next layer of the NN [1, 2].

Figure 2.1: Operation of one node in the NN

$$x = Bias + x_1 \times w_1 + x_2 \times w_2 + x_3 \times w_3 \tag{2.1}$$

where *Bias* is the bias value,  $x_1, x_2$ , and  $x_3$  are the inputs, *Weight1* and *Weight2* are the weights, x is the input for the activation function.

$$y = \frac{1}{1 + e^{-x}} \tag{2.2}$$

where y is the output data after the activation function.

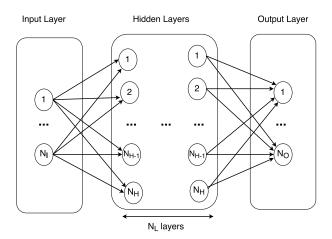

The NN is shown in Fig. 2.2. This NN has  $N_I$  nodes in the input layer,  $N_O$  nodes in the output layer,  $N_H$  nodes in one hidden layer, and  $N_L$  hidden layers.

Figure 2.2: Architecture of the NN

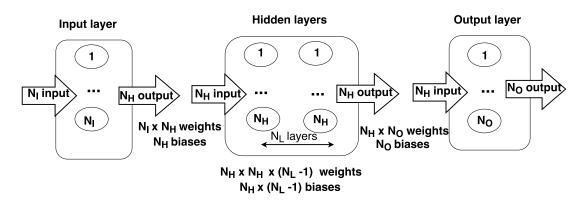

Fig. 2.3 shows the weights and biases in each layer of the NN. This NN has  $N_I \times N_H$  weights and  $N_H$  biases in the connections between the input layer and the first layer of the hidden layers. The connections between the last layer of the hidden layers and the output layer have  $N_H \times N_O$  weights and  $N_O$  biases. The connections inside the hidden layers have  $(N_H + 1) \times N_H \times (N_L - 1)$  weights and  $N_H \times (N_L - 1)$  biases.

Figure 2.3: Weights and biases of the NN

In this study, two types of the NN are used. The first NN type has one hidden layer  $(N_L = 1)$  and the second type of the NN has two hidden layers  $(N_L = 2)$ . The  $N_{D1}$  number of weights and biases for one hidden layer NN is calculated in Eq. (2.3).

$$N_{D1} = (N_I + 1) \times N_H + (N_H + 1) \times N_O \tag{2.3}$$

The calculation of  $N_{D2}$  weights and biases for the two hidden layers NN is illustrated in Eq. (2.4).

$$N_{D2} = (N_I + 1) \times N_H + (N_H + 1) \times N_H + (N_H + 1) \times N_O$$

(2.4)

### 2.2 Particle swarm optimization algorithms in previous studies

#### 2.2.1 Standard particle swarm optimization algorithm

The SPSO algorithm is a well-known method for training of the NN. The idea behind the SPSO algorithm comes from the social behaviors such as a bird flocking or a fish schooling. At any given time t, each particle p in the swarm tends to move to the best personal position found by this particle and the best global position of the swarm. The best global position is evaluated from the best personal position of all particles in the swarm [3, 4]. The operation of the SPSO algorithm can be described as follows.

- 1. Initialize the random value for all particles in the swarm at time t. For example, particle p has position  $\overrightarrow{xp}(t)$ , velocity  $\overrightarrow{vp}(t)$ , best personal position  $\overrightarrow{xPbestp}(t)$ , best global position  $\overrightarrow{xGbest}(t)$ . The fitness value for the best personal position  $\overrightarrow{xPbestp}(t)$  is  $Pbest_p(t)$ . In a similar way, the fitness value for the best global position  $\overrightarrow{xGbest}(t)$ .

- 2. Calculate the new velocity at time (t + 1) according to Eq. (2.5).

$$\vec{v_p}(t+1) = w \times \vec{v_p}(t) + c_1 \times r_1 \times (\overrightarrow{xPbest_p}(t) - \vec{x_p}(t)) + c_2 \times r_2 \times (\overrightarrow{xGbest}(t) - \vec{x_p}(t))$$

(2.5)

where w is the inertia weight,  $r_1$  and  $r_2$  are the random numbers,  $c_1$  and  $c_2$  are the coefficients,  $\overrightarrow{xPbest_p}$  is the best personal position found by particle p,  $\overrightarrow{xGbest}$ is the best position found by any particle in the swarm

3. Evaluate the new position at time (t+1) based on Eq. (2.6).

$$\overrightarrow{x_p}(t+1) = \overrightarrow{x_p}(t) + \overrightarrow{v_p}(t+1)$$

(2.6)

4. Estimate the new fitness values at time (t + 1) based on Eqs. (2.7) and (2.8). The positions corresponding to these new fitness values are also discovered. As presented, the best personal position  $\overrightarrow{xPbest_p}(t+1)$  is the position that obtains the fitness value  $Pbest_p(t+1)$ , and the best global position  $\overrightarrow{xGbest}(t+1)$  is the position that achieves the fitness value Gbest(t+1).

$$Pbest_p(t+1) = \begin{cases} f(\overrightarrow{x_p}(t+1)) & if \ f(\overrightarrow{x_p}(t+1)) < Pbest_p(t) \\ Pbest_p(t) & if \ f(\overrightarrow{x_p}(t+1)) \ge Pbest_p(t) \end{cases}$$

(2.7)

where f(.) is a fitness function.

$$Gbest(t+1) = \underset{p}{\operatorname{argmin}} Pbest_p(t+1)$$

(2.8)

5. The stopping criterion is checked. In the PSO algorithm, the stopping criterion could be a number of iterations or a threshold of the global fitness value *Gbest*. If the stopping condition is satisfied, the PSO algorithm is stopped. Otherwise, the operation of the SPSO algorithm returns to step 2 to continue a new iteration at time (t + 2).

#### 2.2.2 Dissipative PSO algorithm

The SPSO could be trapped by a local minimum. In this situation, the PSO algorithm will be stopped. If the SPSO sticks to the local minimum during the training of the NN. The NN cannot be trained. The recognition rate of the testing phase will be low, and the learning error of the training phase will be high. A well-known algorithm was created to overcome the premature convergence called the dissipative PSO algorithm [5]. This is the simple variation of the SPSO algorithm which adds Eqs. (2.9) and (2.10) after calculating the new velocity  $\vec{v_p}(t+1)$  and the new position  $\vec{x_p}(t+1)$ .

$$If(rand() < c_v) \ Then \ \overrightarrow{v_p}(t+1) = rand() \times \overrightarrow{v_{max}}$$

$$(2.9)$$

$$If(rand() < c_l) Then \vec{x_p}(t+1) = Rand(lo, up)$$

$$(2.10)$$

$c_v$  and  $c_l$  are numbers in the range [0, 1], Rand(lo, up) is the random number between [lo, up], rand() is the random number in the range [0, 1], and  $\overrightarrow{v_{max}}$  is the maximum velocity.

### 2.3 NN trained by the PSO algorithms

For the training of the NN by PSO algorithms, one important aspect is the encoding strategy. In this approach, the weights and the biases of the NN are encoded in the particle of the PSO algorithm.

For encoding, the position  $\vec{x_p}$  of particle p in the swarm is considered as a vector which represents all weights and biases of the NN. If the PSO training has P particles, Pvectors will be used in the training phase. In this situation, the number of weights and biases in the NN equals to the number of dimensions of one particle vector. Each element of the vector corresponds to one parameter of the NN. When the elements of PSO vector are changed during the PSO algorithm, the corresponding parameters of the NN are also updated [6, 7].

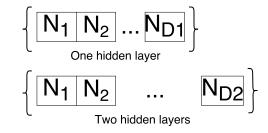

As presented in the previous section, two different type NNs are investigated in this research. The first NN has one hidden layer and  $N_{D1}$  parameters. The calculation of  $N_{D1}$  parameters is shown in Eq. (2.3). The second NN is two-hidden-layer NN which has  $N_{D2}$  weights and biases which are described in Eq. (2.4). Therefore, there are two different encoding vectors. The first vector is  $N_{D1}$ -dimensional vector and the second vector has  $N_{D2}$  dimensions. These encoding vectors are illustrated in Fig. 2.4.

Figure 2.4: Encoding vectors for one PSO particle in two different types of NN

For demonstration, the details of the encoding vector for two-hidden-layer NN can be observed in Fig. 2.5. The  $N_{D2}$  parameters contain  $N_I \times N_H$  weights and  $N_H$  biases in the connections between the input layer and the first hidden layers,  $N_H \times N_H$  weights and  $N_H$  biases in the connections between the first hidden layer and the second hidden layer,  $N_H \times N_O$  weights and  $N_O$  biases in the connections between the last layer of the hidden layers and the output layer.

Finishing the encoding procedure, the training phase is executed. The training data are sent to the NN whose weights and biases are already encoded in the form of the PSO vectors. Each PSO vector represents a position of a particle. This position is a set of potential solutions for the parameters (the weights and the biases) of the NN. The goal of the training phase is to find the position of the particles, in other words, the weights and biases of the NN which could minimize the error between the actual output of the NN and the desired output of the NN.

In each iteration, the actual output data of the NN are compared with the labeled data (the desired output data) using an objective function, for all data. In this research, the mean square error function is used as the objective function as shown in Eq. (2.11). This is the single objective function [8].

Figure 2.5: Details of the encoding vectors for two-hidden-layer NN

$$fitness_p = \frac{1}{T} \sum_{i=1}^{T} (labeled_data_i(j) - output_data_{ip}(j))^2$$

(2.11)

where  $fitness_p$  is the fitness value of particle p, T is the number of training samples,  $labeled\_data_i(j)$  is the  $j^{th}$  component of the labeled data i  $(1 \le i \le T)$ ,  $output\_data_{ip}(j)$ is the  $j^{th}$  output data i of particle p.

At any given iteration, for each particle p, the position ever visited by this particle which has the lowest learning error (lowest fitness value  $fitness_p$ ) calculated by Eq. (2.11) becomes the personal best position  $\overrightarrow{xPbest_p}$ . The fitness value corresponds to the personal best position becomes the personal best fitness value  $Pbest_p$ . In the similar way, the position visited by all particles in the swarm that obtains the lowest learning error calculated by Eq. (2.11) is the global best position  $\overrightarrow{xGbest}$  of the swarm. The corresponding fitness value of the global best position is the global best fitness value Gbest.

The particles move in each iteration to minimize the objective function (Eq.2.11). The changing of the position of each particle means the weights updating and the biases

updating of the NN.

The training continues until the achievement of the stopping conditions. Normally, the stopping conditions are the number of iterations or the final global fitness value *Gbest*. The weights and biases of the NN which correspond to the global best position of the PSO algorithm after the training phase is used in the testing phase of the NN.

#### References

- S. Haykin. Neural networks and learning machines. Pearson Education, Upper Saddle River, NJ, third edition, 2009.

- [2] S. Haykin. Neural Networks: A Comprehensive Foundation. Prentice Hall PTR, Upper Saddle River, NJ, USA, 2nd edition, 1998.

- [3] J. Kennedy and R. Eberhart. Particle swarm optimization. In Proceedings of the IEEE International Conference on Neural Networks, volume 4, pages 1942–1948, Nov 1995.

- [4] R. Poli, J. Kennedy, and T. Blackwell. Particle swarm optimization. Swarm Intelligence, 1(1):33–57, 2007.

- [5] X. F. Xie, W. J. Zang, and Yang Z. L. Dissipative particle swarm optimization. In *Proceedings of the 2002 Congress on Evolutionary Computation*, volume 2, pages 1456–1461, 2002.

- [6] J. R. Zhang, J. Zhang, T. M. Lok, and M. R. Lyu. A hybrid particle swarm optimizationback-propagation algorithm for feedforward neural network training. *Applied Mathematics and Computation*, 185(2):1026 – 1037, 2007.

- [7] M. T. Das and L. C. Dulger. Signature verification (sv) toolbox: Application of pso-nn. Engineering Applications of Artificial Intelligence, 22(45):688 – 694, 2009.

- [8] E. L. Lehmann and G. Casella. Theory of Point Estimation, Second Edition Springer Texts in Statistics, volume 41. 1998.

### Chapter 3

## Proposed PSO algorithms

Chapter 3 focuses on the premature convergence issue of the SPSO algorithm by proposing three improved versions of the SPSO algorithm called wPSOd\_CV, PSOseed, and PSOseed2. Several parts of this chapter have been published in our research articles [1, 2].

#### 3.1 Introduction

In the training of the NN, the SPSO algorithm may be stuck in a local minimum. In this situation, the SPSO will be stopped, the NN cannot be trained, and the recognition rate will be low. Therefore, it is necessary to have an improved version of the SPSO algorithm to solve the premature convergence of this algorithm.

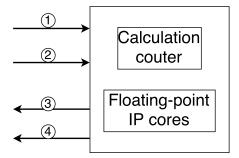

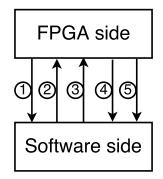

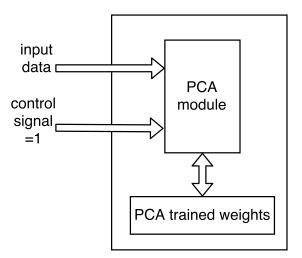

Several different approaches have been introduced to overcome the premature convergence of the PSO algorithm. The attractive and repulsive PSO (ARPSO) adds the repulsive phase. The diversity of the swarm calculated in each iteration of the swarm to determine whether the ARPSO operates in the attractive phase (the SPSO algorithm) or the repulsive phase [3]. The PSO with spatial particle extension (SEPSO) that adds the radius r to detect the collisions of all particles in the swarm. If the collisions occur, the particles will be bounced backward to prevent the situation when all particles stick to the local minimum [4]. The opposition-based PSO calculates the opposite particle of each particle in each iteration. If the opposite particle has a better fitness function than the original particle, this opposite particle will replace the original particle [5]. Other researchers use the multi-swarm strategy [6] or use not only the information of a particle but also the information of its neighborhood to calculate the new position of this particle [7]. Other solutions are to use the mutation operations such as the Cauchy mutation [8, 9], the Gaussian mutation [10, 11], or to combine the SPSO algorithm with the genetic algorithm [12]. The improved versions of the PSO in previous studies normally add more functions, more compute-intensive tasks to the SPSO algorithm. It is beneficial to investigate an improved version of the PSO algorithm to keep the particles out of the local minimum which does not add many functions or tasks to the SPSO algorithm.