# DSPデジタル制御電源の入出力電圧変更にともなうループゲイン変化対策

野崎幸弘 前川峻徳 (新電元工業株式会社) 竹田史章(高知工科大学) 曽禰元隆(DSP 応用技術研究所)

The Method of Countermeasure of Changed Loop Gain by Input-Output Voltage Change for DSP Digital Controlled POL

Yukihiro Nozaki , Michisato Maekawa(Shindengen Electric MFG.CO.,LTD) Fumiaki Takeda(Kochi University of Technology) Mototaka Sone(DSP Application Technology Lab.)

キーワード スイッチング電源, POL, デジタル制御, 高速応答

# <1> まえがき

Pentium や FPGA などは消費電力低減の要求から、低電 圧大電流化の方向へと進化している。また、動作速度の高 速化のため、動作クロックも数 GHz と高速である。このような 高速電流変動負荷に対して、現在では Point of Load (以下 POL)と呼ばれる電源で対応している。POL を用いた給電体 系は、まず、48V付近のバス電圧をIBAと呼ばれる中間電 源で12V程度に降圧し、更にPOLで負荷が所望する電圧 である 1V から 5V に降圧する[1]。ここで、POL に入力され る電圧は 12V であることが多いが、低いものでは 5V で用 意されるものもある。また、IBA 用の電源は非制御で使われ ることが多く,出力電圧範囲は8~14Vなどと広く、精度も± 10%と POL と比べて一桁悪い。このような電源から電力の 供給を受ける POL は入力電圧範囲を広く、また、稼動中の 入力変動も考慮した電源である必要がある。また、 出力電 圧においてもCPUのコア電圧は統一されていないため、出 力電圧の変更も可能でなければならない。

入力電圧の変動に対して、現在は電流モードによって対応している。電流モードとは、インダクタ電流をフィードバック制御に加えることによって、より安定に制御する方法である。インダクタ電流波形が入力電圧によって変化することから、搬送波の傾きをインダクタ電流によって可変させることで、入力電圧の影響をキャンセルする方法[2][3]である。この方法においては、入力電圧が高いときには三角波の傾斜を緩やかにすることで、デューティの変動幅を入力電圧によっても調整している。一方、出力電圧変更に対しては、ボリューム抵抗によって任意の出力電圧に設定するか、抵抗を付加する方法がある。ボリューム抵抗による設定では出力電圧の変更が容易であるという利点があり、抵抗を付加する方

法では出力電圧の調整が容易であるという利点がある。

このようなアナログ制御 POL に対して、出力電圧変更方 法においては大きな問題がある。まず、ボリューム抵抗によ って出力電圧を変更する方法においては、設定する出力 電圧の変更にともない、フィードバックゲインも変更される。 これは、出力電圧を分圧して制御回路に入力するため、目 標電圧との差が同じでも分圧比によって制御回路に入力さ れる偏差が異なるためである。一方、抵抗を付加する方法 においては、抵抗値変更にともなうフィードバックゲインの 変更に加え、出力電圧の変更が困難という問題がある。こ れらの問題に対して DSP によるデジタル制御では、リファ レンス電圧を容易に変更可能であるため、分圧抵抗によっ て出力電圧の変更をする必要がない。つまり、プログラムを 書き換えるだけでゲイン変更をともなわない出力電圧の変 更を期待できる。また,入力電圧の変動に対しても,制御中 において制御ゲインの変更が可能である DSP デジタル制 御ならばソフトウェアにおいて対応可能であると期待され 3.

本論文では代表的なアナログ制御電源と DSP デジタル制御電源を比較し、それぞれの優劣を述べる。出力電圧が変更された場合においては、アナログ制御はフィードバックゲインの変更を必要としたが、DSP デジタル制御においてはフィードバックゲインの変更を必要としない。一方、入力電圧が変更された場合においては、電流モードアナログ制御電源においてはフィードバックゲインの変更を必要としないのに対し、DSP デジタル制御電源ではフィードバックゲインの変更を必要とする。しかし、DSP デジタル制御電源においては入力電圧によって制御ゲインを調整することによって入力電圧の影響を受けないようにした。これによってDSP デジタル電源の長所を明らかにし、短所についても簡

単な補正プログラムを追加することによって補った。

#### <2> 方法

#### <2-1> 制御回路

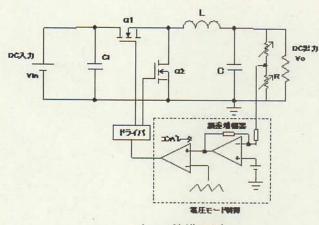

本論文で用いた制御回路を図 1(a,b)に示す。なお、同図(a)はアナログ制御回路によるもので、同図(b)はデジタル制御回路である。アナログ制御回路は同図(a)に示される通り、主回路と制御回路に分けられる。主回路は入力電圧をコンデンサで平滑化し、ハイサイドの MOSFETで所望の出力電圧となるように制御回路で決定された矩形波が出力される。その矩形波はコイルによって電流が平滑化され、コンデンサによって電圧が平滑化され、出力される。一方、制御回路は分圧された出力電圧が誤差増幅器に入力され、その出力と搬送波とがコンパレータによって比較された結果、搬送波より大きければMOSFETをオンする。このとき、分圧抵抗によって分圧比を変更することによってフィードバックゲインが変更される。また、この同図(a)は電圧モードアナログ回路図

(a) アナログ制御回路

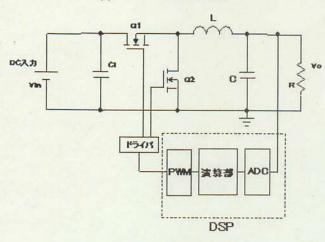

(b) デジタル制御回路 図1 POL 用電源制御回路

であるが、電流モードにおいてはLの電流によって搬送 波の波形が変化する。

デジタル制御回路は、アナログ制御回路をデジタルに 置き換えることによって実現可能である。しかし、主回 路においては同図(b)に示されるように分圧抵抗が不要 である。これは DSP 内部のリファレンス電圧を変更する ことによって出力電圧の変更が可能であるためである。 制御回路においては検出を ADC によりアナログ信号を デジタル信号に変換する。その信号を DSP 演算部によっ て操作量の算出を行い、PWM を発生させる。その信号 によってドライバ IC を駆動させるところからはアナロ グ制御と同様である。ただし、デジタル制御回路を設計 する際には、ADC のサンプリング時間、演算時間、PWM の精度に注意する必要がある。高速応答性を得るために は、制御周期は2usec~1usecほど必要になる。そのため、 ADC の変換速度が最速 320nsec, PWM の精度が 150psec である TI 社製の TMS320F2808(以下 F2808)を使用する ことにした。

### <2-2>PWM 精度による安定性の評価

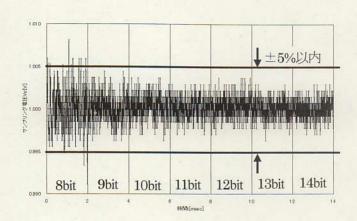

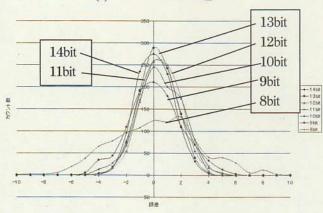

前節において、デジタル制御電源で注意しなければならないものとしてPWMパルスの精度を挙げたので、具体的に何nsec 必要なのかを示す。従来、PWMの最小パルス幅はDSPのクロック周波数に依存するため、電源のスイッチング周波数を上げていくにつれPWM精度は落ち、電源の出力電圧が波打つ現象であるリミットサイクルオシレーションを生じ、動作が安定しなくなる。そこで、デジタル制御回路のPWM精度による波形の安定性評価を行う。DSPで実現できるPWM精度はスイッチング周波数500kHz 時で最大14bit である。よって、測定を行なう精度は一般的なPWM精度である8bit からF2808の最大精度である14bitまで行なった。評価は制御時におけるADCからの入力信号を1周期に1回、連続1000個サンプリングし、目標電圧との差をカウントする方法を用いた。

測定結果を図 2(a,b)に示す。なお,同図(a)は各ビット長における出力電圧のサンプリング結果,同図(b)はサンプリング結果の分布図である。サンプリングは制御周期2usecに1回,2msecずつ行なった。結果は8bitの場合において評価基準の一つである±5%以内という条件を満たすことが出来なかったが9bit以上では基準値を満足しており、PWMの精度は9bit以上必要であることが分かる。なお、9bit以上の精度において、その効果を判断出来ないので、より詳細に評価するため誤差分布を調べる。

(b) サンプリング電圧の誤差分布 図2 ビット長に対する出力電圧の安定性

誤差分布は横軸の中心が目標値Vrefとの誤差をあらわし、縦軸がそのカウント数をあらわす。つまり、中心誤差0で高く、細い結果が制御結果が安定しており良い結果であると言える。よって、PWM 精度による安定性は同図(b)に示される通り 14bit が一番よく、ビット長を減らしていくにつれ悪くなり、8bit が一番悪い結果となった。ただし、9bit から 14bit まではそれ程大差はなく、8bit の結果と 9bit の結果に大きな差があることが示される。これは同図(a)の結果と同様である。ここで、8bit ではPWM の精度が 10nsec であり、9bit では 5nsec である。この結果から、POL 用制御 DSP には最低 5nsec 制度のPWM が必要であることが分かる。今回使用する DSP は最大 14bit まで精度が出せるのでこの条件を満足している。以降、PWM の制度は 14bit で実験を行なう。

<3> 結果及び検討

<3-1> 出力電圧の制御結果への影響

アナログ制御回路において、出力電圧を変更する方法

は負荷電圧の分圧比を変更するのが一般的である。一方, デジタル制御回路ではDSPの内部リファレンス電圧を 変更することで出力電圧の変更が可能である。そこで, アナログ制御回路における出力電圧の変更方法とDSP デジタル制御における出力電圧の変更方法で制御を行い, その影響を明らかにする。なお,入力電圧は一般的な POLと同様に12V一定とし,出力電圧も同様に1.0V, 1.8V, 2.5Vとした場合の過渡応答時の出力電圧変動値で 評価を行なう。

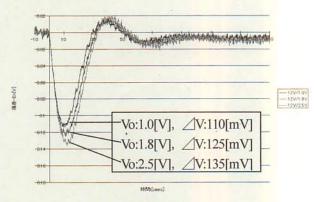

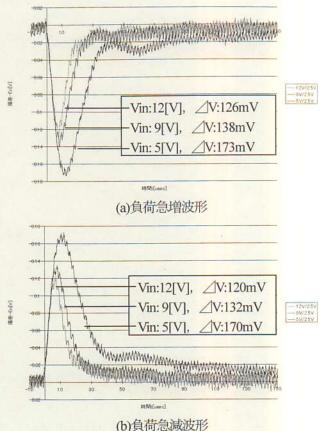

アナログ制御回路における出力電圧による制御結果への影響を図 3(a,b)に示す。なお、同図(a)は負荷急増時の波形、同図(b)は負荷急減時の波形である。負荷急増時においては同図(a)より、出力電圧によって異なる V値を示した。出力電圧 Vo が 1.0V の場合に V が 110mV と最も小さく、2.5Vで V が 135mV と最も大きくなった。一方、負荷急減時においては同図(b)より、負荷急増時とは逆の結果となり、出力電圧 Vo が 1.0V の場合に V が 170mV と最も大きく、2.5Vで V が 165mV と最も小さくなった。

(a)負荷急增波形

(b)負荷急減波形 図3 検出電圧の分圧による出力電圧変更

出力電圧によって負荷急変時の過渡応答が異なる原因 は負荷電圧を分圧して制御回路に入力しているためだと 考えられる。アナログ制御回路においては出力電圧の目 標値であるリファレンス電圧が一定であるため、負荷の 分圧抵抗の分圧比を調節して所望の出力電圧を得る。例 えば、リファレンス電圧が 1.0V の場合、出力電圧を 1.0V に設定する場合は分圧する必要がないが、出力電圧を 1.8V とする場合は 5/9 に、2.5V にする場合は 2/5 に降 圧して誤差増幅器に入力する必要がある。この時に実際 の電圧値より誤差が小さくなるのでフィードバックゲイ ンも減少する。これは負荷急減時にも当てはまるはずだ が,同図(b)に示される通り負荷急増時とは逆の結果とな っている。この差は、急減時におけるデューティが最小 値で制御しているためだと考えられる。そのため、定常 時においてデューティ幅が一番狭い 1.0V が一番 △V 値 が大きくなったと考えられる。急増時と比較して△Vの 値も大きく出ていることもそう考えられる理由である。

分圧抵抗によって出力電圧を変更するアナログ制御回路の方法に対して DSP デジタル制御回路での出力電圧変更方法での制御結果を明らかにする。デジタル制御において出力電圧の変更方法は内部リファレンスを変更することによって可能である。内部リファレンス電圧はプログラム内に記述された値であり、プログラムを書き換えることで変更される。

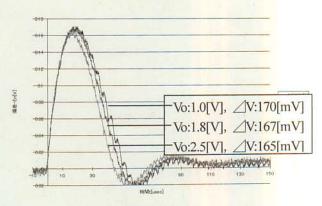

DSP デジタル制御 POL において出力電圧を変更した場合を図 4(a,b)に示す。なお、同図(a)に負荷急増波形を,同図(b)に負荷急減波形を示す。負荷急増波形は同図(a)に示される通り、出力電圧が 1.0V 出力時に ДV が 110mV で最小となり、2.5V 出力時に ДV が 129mV で最大となった。この結果からデジタル制御回路においても図 3(a)のアナログ制御回路と同様の結果を示しているように思われるかもしれない。しかし、デジタル制御回路のおける ДV の差はチョッパコイルの容量によるリップルによるもので、フィードバックゲインの変化によるものではないと考えられる。

同様に負荷急減時の波形は図 4(b)に示されるように出力電圧が 1.0V 出力時に V が 107mV と最小となり、2.5V 出力時に V が 120mV で最大となった。負荷急減時においても V の最大値と最小値で差が出たが、負荷急増時と同様にリップルの影響を受けたためだと考えられる。以上の結果からアナログ制御回路の分圧抵抗による出力電圧の変更方法においてはフィードバックゲインが変わり制御結果にも影響を与えたが、DSP デジタル制御による内部リファレンスを変更して出力電圧を変更する方法においてはフィードバックゲインを変えることな

(b)負荷急減波形 図4 リファレンス電圧による出力電圧の変更

##Mt[usec]

MATHEMANAMENTERS

く出力電圧変更の影響をほとんど受けずに制御可能であることが分かった。

#### <3-2> 入力電圧の制御結果への影響

POL においては出力電圧の変更だけでなく、入力電圧の変更にも対応する必要がある。そこで、入力電圧を変更した場合の電流モードアナログ制御回路での制御結果と DSP デジタル制御回路での制御結果を比較し、その違いを明らかにする。なお、実験条件は出力電圧を 2.5V一定とし、入力電圧を 12V、9V、5V とした。

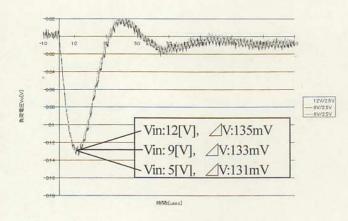

電流モードアナログ制御回路による制御結果を図5(a,b)に示す。なお、同図(a)に負荷急増波形を、同図(b)に負荷急減波形を示す。負荷急増時における制御結果は同図(a)より入力電圧が12Vのときに△Vが最も小さく131mVであった。波形が同一の軌跡を描いて収束しているため、△Vの差はリップルの差によるものと考えられ、フィードバックゲインは変化していないものと考えられる。同様に、負荷急減波形の結果も同図(b)に示される通り、入

# (a) 負荷急增波形

(b) 負荷急減波形 図5 アナログ制御回路電流モード制御波形

力電圧が 12V から 5V の場合で同一である。ただ、負荷 急増時と比較すると V の値に大きな違いがあるため、 負荷急減時においてはデューティ最小値で制御しており、 制御が十分に効いていない結果であると考えられる。

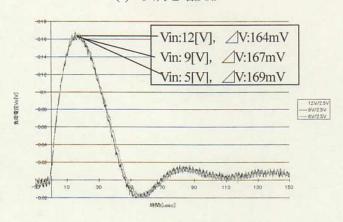

一方、DSP デジタル制御回路によって制御結果を図 6(a,b)に示す。なお、同図(a)に負荷急増波形を、同図(b)に負荷急減波形を示す。負荷急増波形は同図(a)に示される通り入力電圧を変更すると V の値も変化することが示される。 V の値は入力電圧 12V のときに 126mV で最小となり、入力電圧 5V のときに 173mV で最大となった。この V の差はリップルの影響だけでなく、フィードバックゲインの影響を大きく受けているためであると考えられる。同様に、負荷急減波形も同図(b)に示される通り V の値は入力電圧 12V のときに 120mV と最小になり、入力電圧 5V のときに 170mV と最大になった。この理由としては、デューティの変動幅は出力電圧と目標値との差から算出され決定されるが、同じ変動幅であっても、入力電圧によって出力電圧の変動幅が異なるためである。

図6 入力電圧変更によるデジタル制御結果

以上の結果から、電流モードで制御を行なう場合には 入力電圧の影響はほとんど受けることがない。しかし、 DSPデジタル制御などの電圧モードによる制御では入力 電圧の影響を受け、制御結果も影響を受ける。そのため、 入力電圧を考慮した電源を設計する場合には、入力電圧 範囲の中心でチューニングを行ない入力電圧による影響 を最小限にするか、入力電圧が変更されるごとに再チューニングすることが考えられる。しかし、プログラマーブルなデジタル制御であっても、電流モードによるアナログ制御回路と比較すると大きな手間となる。そこで、デジタル制御において入力電圧の影響を打ち消すアルゴリズムを考案する必要がある。

#### <3-3> 入力電圧の制御結果への対策

DSPデジタル制御においては入力電圧によって制御結果に差が生じることを前節で示した。そこで、本節ではその対策を行なう。

入力電圧と出力電圧の関係は式(1)のように示される。 入力電圧が制御結果に与える影響は式(1)より入力電圧 の比例の関係にある。そこで、△Duty に 1/Vin を掛ける ことにより入力電圧の影響をキャンセルすることを考え

る。 ∠Duty は式(2)の制御係数 K0, K1, K2 と偏差 E で構成される PID 制御式で与えられるので、それぞれの制御係数に入力電圧の逆数を掛け合わせることによって入力電圧の影響を打ち消すことができる。

$$\triangle$$

Vout =  $\triangle$ Duty × Vin ....(1)

$$\triangle Duty = K0*E[n] + K1*E[n-1] + K2*E[n-2] \cdot \cdots \cdot (2)$$

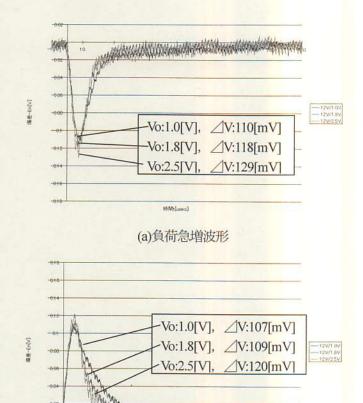

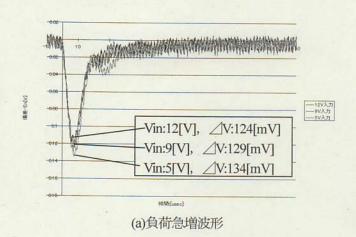

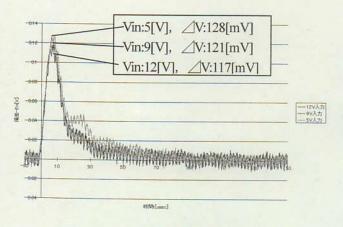

入力電圧の影響対策制御結果を図7に示す。なお、同図(a)に負荷急増波形を、同図(b)に負荷急減波形を示す。 負荷急増時は、△Vの最大値はVinが5Vの場合で134mV、 最小値は△Vが12Vの場合で124mVとなった。この差は10mVであり、対策前の47mVと比較すると大きく改善されたことが分かる。同様に負荷急減時においても、 △Vの最大値は5V制御時の128mV、最小値は12V制御時の117mVであり、その差は11mVと対策前の50mVから大きく改善されたことが分かる。

(b)負荷急減波形 図7 入力電圧ゲイン補正制御結果

以上のことから、DSP デジタル制御においても、入力 電圧を監視することにより入力変動に対応することが可 能である。

### <4> まとめ

本論文では POL の入出力電圧がコントローラに与える影響を明らかにし、その対策を DSP デジタル制御によって行なった。出力電圧の変更に対しては、アナログ制御回路は影響を受けるがデジタル制御の場合は影響をほとんど受けずに制御可能である。一方、入力電圧の変更に対しては、アナログ制御の場合は電流モードによって対応可能だが、デジタル制御では影響を大きく受けてしまう。そこで、デジタル制御においても入力電圧の影響を打ち消すようなアルゴリズムを提案し、その効果を示した。

#### 参考文献

- [1] 汎用電源にデジタル化の波 / 川村祥子 / 2006.3 EDN Japan

- [2] 電流モード制御DC-DC コンバータの特性改善 / Claude Abrahm/ 2007. 1 EDN Japan

- [3] Switching Power Supply Design / Abraham I. Pressman / McGraw-Hill / 1998

# 著者紹介 野崎 幸弘 (正会員)

1987年3月東京電機大学電気工学科卒業。同年4月新電元工業入社。システム製品の開発設計を担当し、その後回路技術の研究開発職に従事、現在に至る。電気学会会員。

前川 峻徳

2007 年 3 月武蔵工業大学大学院工学研究科 電気工学専攻修士課程修了。同年 4 月新電 元工業入社。回路技術の研究開発職に従事、 現在に至る。

竹田 史章 (正会員) 論文p48 参照

曽禰 元隆 (正会員) 論文 p48 参照